- 您现在的位置:买卖IC网 > PDF目录10253 > CS8420-CSZ (Cirrus Logic Inc)IC SAMPLE RATE CONVERTER 28SOIC PDF资料下载

参数资料

| 型号: | CS8420-CSZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 60/94页 |

| 文件大小: | 0K |

| 描述: | IC SAMPLE RATE CONVERTER 28SOIC |

| 标准包装: | 27 |

| 类型: | 采样率转换器 |

| 应用: | CD-R,DAT,DVD,MD,VTR |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC |

| 包装: | 管件 |

| 产品目录页面: | 759 (CN2011-ZH PDF) |

| 配用: | 598-1782-ND - EVALUATION BOARD FOR CS8420 |

| 其它名称: | 598-1125-5 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页当前第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页

DS245F4

63

CS8420

13.4

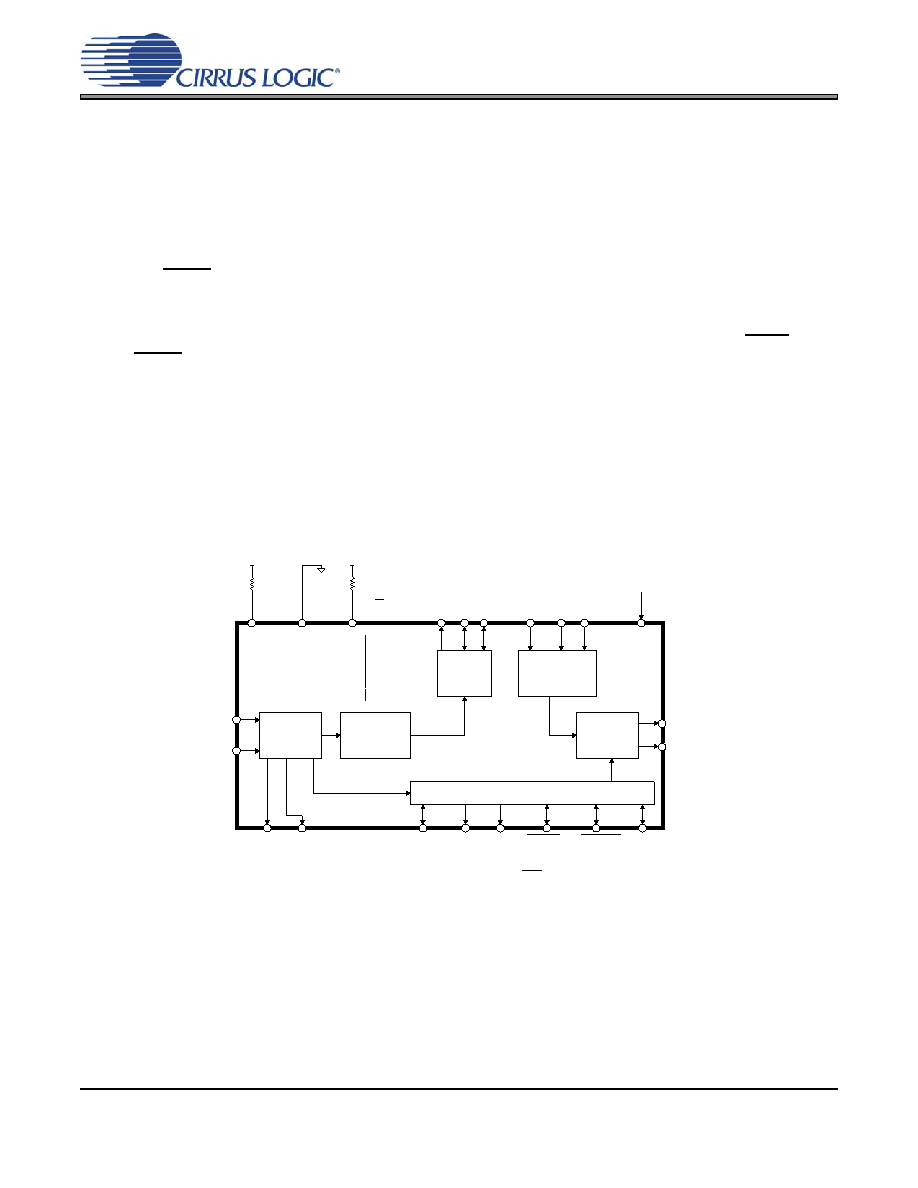

Hardware Mode 3 Description

(Transceive Data Flow, with SRC)

Hardware Mode 3 data flow is shown in Figure 26. Audio data is input via the AES3 receiver, and rate con-

verted. The audio data at the new rate is then output via the serial audio output port. Different audio data,

synchronous to OMCK, may be input into the serial audio input port, and output via the AES3 transmitter.

The channel status data, user data, and validity bit information are handled in two alternative modes: 3A

and 3B, determined by a start-up resistor on the COPY pin. In mode 3A, the received PRO, COPY, ORIG,

and AUDIO channel status bits are output on pins. The transmitted channel status bits are copied from the

received channel status data, and the transmitted U and V bits are zero.

In mode 3B, only the COPY, and ORIG pins are output, and reflect the received channel status data. The

transmitted channel status bits, user data, and validity bits are input serially via the PRO/C, EMPH/U, and

AUDIO/V pins. Figure 20 shows the timing requirements.

The serial audio input port is always a slave.

If a validity, parity, bi-phase, or lock receiver error occurs, the current audio sample will be held.

Start-up options are shown in Table 12, and allow choice of the serial audio output port as a master or slave,

whether TCBL is an input or an output, the serial audio ports formats, and the source of the transmitted C,

U, and V data. The following pages contain the detailed pin descriptions for Hardware mode 3.

AES3

Encoder

&Tx

Serial

Audio

Output

AES3 Rx

&

Decoder

Sample

Rate

Converter

C & U bit Data Buffer

Clocked by

Output Clock

Clocked by

Input Derived Clock

RXP

RXN

OLRCK

OSCLK

SDOUT

TXP

TXN

RMCK RERR

COPY ORIG EMPH/U AUDIO/V TCBL

DFC0

DFC1

VD+

H/S

Output

Clock

Source

OMCK

Power supply pins (VD+, VA+, DGND, AGND) & the reset pin (RST) and the PLL filter pin (FILT)

are omitted from this diagram. Please refer to the Typical Connection Diagram for hook-up details.

VD+

Serial

Audio

Input

ILRCK

ISCLK

SDIN

PRO/C

Figure 26. Hardware Mode 3 - Transceive Data Flow, with SRC

相关PDF资料 |

PDF描述 |

|---|---|

| 15280-18PG-321 | CONN JACK 18POS CABLE PIN |

| CS496112-CQZ | IC DSP 32BIT 8CH SER I/O 144LQFP |

| CS181022-CQZ | IC COBRANET CS181022 144LQFP |

| AD1896AYRSZ | IC CONV SAMPLE RATE ASYNC 28SSOP |

| CS6422-CSZ | IC SPEAKERPHONE ENHANCED 20SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS8420-CSZ/D1 | 制造商:Cirrus Logic 功能描述: |

| CS8420-CSZR | 功能描述:音频 DSP IC Digital Audio Sample Rate Convertr RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| CS8420-CSZR/D1 | 制造商:Cirrus Logic 功能描述: |

| CS8420-DS | 功能描述:音频 DSP Digital Audio Sample Rate Converter RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| CS8420-DSR | 功能描述:音频 DSP IC Digital Audio Sample Rate Convertr RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。