参数资料

| 型号: | CS8952-IQZ |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 19/81页 |

| 文件大小: | 0K |

| 描述: | IC TXRX 100/10 PHY 100TQFP |

| 标准包装: | 90 |

| 类型: | 收发器 |

| 规程: | MII |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-TQFP(14x14) |

| 包装: | 托盘 |

| 产品目录页面: | 759 (CN2011-ZH PDF) |

| 其它名称: | 598-1208 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页

CS8952

CrystalLAN 100BASE-X and 10BASE-T Transceiver

26

DS206F1

STATUS Pins

-

COL - Collision indication, valid only for

half duplex modes.

-

CRS - Carrier Sense indication

SERIAL MANAGEMENT Pins

-

MDIO - a bi-directional serial data path

-

MDC - clock for MDIO (16.7 MHz max)

-MII_IRQ - Interrupt indicating change in

the Interrupt Status Register (address 11h)

RECEIVE DATA Pins

-

RXD[3:0] - Parallel data output path

-

RX_CLK - Recovered clock output

-

RX_DV - Indicates when receive data is

present and valid

-

RX_ER - Indicates presence of error in re-

ceived data

-

RX_EN - Can be used to tri-state receiver

output pins

TRANSMIT DATA Pins

-

TXD[3:0] - Parallel data input path

-

TX_CLK - Transmit clock

-

TX_EN - Indicates when transmit data is

present and valid

-

TX_ER - Request to transmit a 100BASE-

T HALT symbol, ignored for 10BASE-T

operation.

The interface uses TTL signal levels, which are

compatible with devices operating at a nominal

supply voltage of either 5.0 or 3.3 volts. It is capa-

ble of supporting either 10 Mb/s or 100 Mb/s data

rates transparently. That is, all signaling remains

identical at either data rate; only the nominal clock

frequency is changed.

4.1

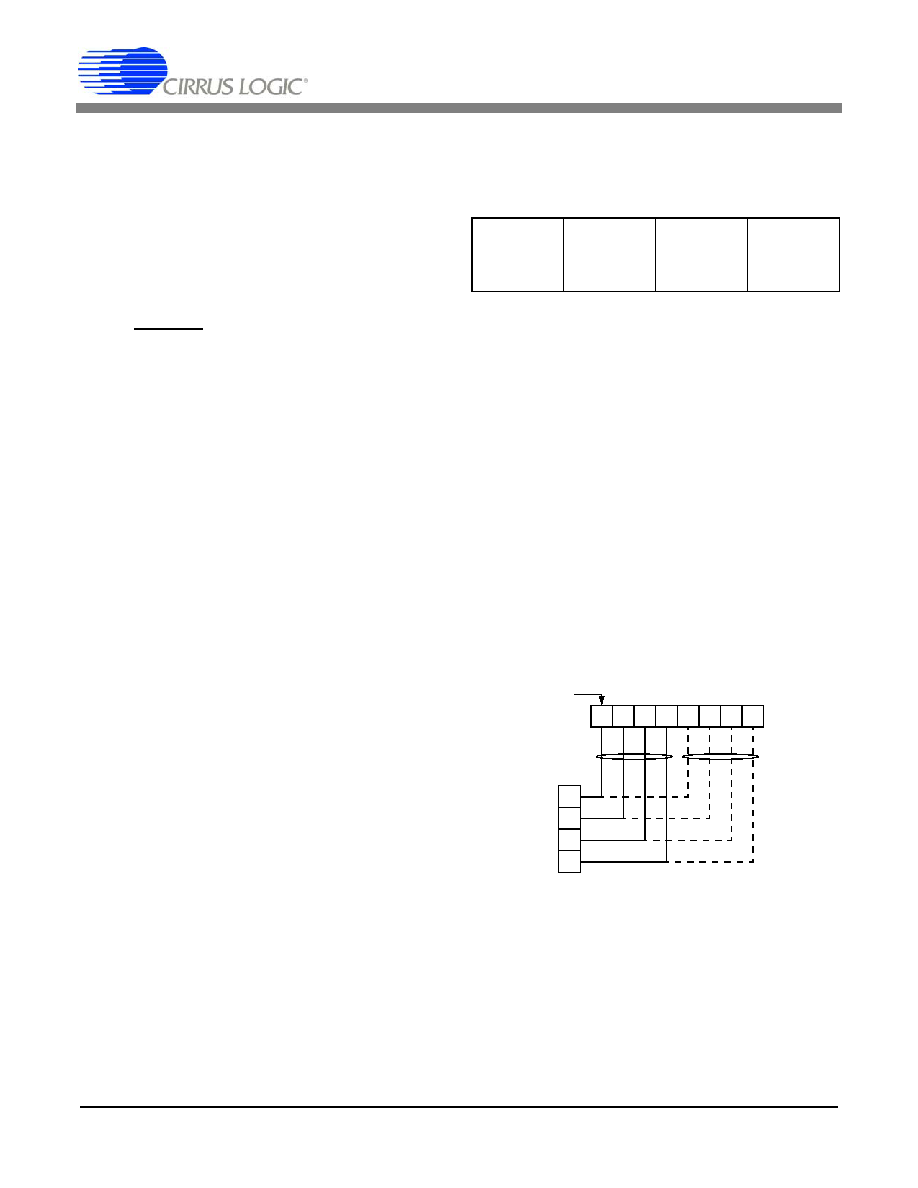

MII Frame Structure

Data frames transmitted through the MII have the

following format:

Each frame is preceded by an inter-frame gap. The

inter-frame gap is an unspecified time during

which no data activity occurs on the media as indi-

cated by the de-assertion of CRS for the receive

path and TX_EN for the transmit path.

The Preamble consists of seven bytes of 10101010.

The Start of Frame Delimiter consists of a single

byte of 10101011.

Data may be any number of bytes.

The End of Frame Delimiter is conveyed by the de-

assertion of RX_DV and TX_EN for receive and

transmit paths, respectively.

Transmission and/or reception of each byte of data

is done one nibble at a time in the following order:

4.2

MII Receive Data

The presence of recovered data on the RXD[3:0]

bus is indicated by the assertion of RX_DV.

RX_DV will remain asserted from the beginning of

the preamble (or Start of Frame Delimiter if pream-

ble is not used) to the End of Frame Delimiter.

Once RX_DV is asserted, valid data will be driven

Preamble

(7 Bytes)

Start of

Frame

Delimiter

(1 Byte)

Data

End of

Frame

Delimiter

MII

LSB

MSB

D0

D1

D2

D3

Nibble

Stream

D0

MAC’s Serial Bit Stream

First Bit

First

Second

Nibble

D1 D2 D3 D4 D5 D6 D7

LSB

MSB

相关PDF资料 |

PDF描述 |

|---|---|

| CY8CLED04DOCD1-56LTXI | IC POWERPSOC DEBUG 4CH 1A 56VQFN |

| CYG2217 | IC MOD PHONE LINE WIRE 1.07" PCB |

| DAC312ER | IC DAC 12BIT MULT HS 20-CDIP |

| DAC8143FPZ | IC DAC 12BIT DAISYCHAIN 16DIP |

| DAC8228FSZ | IC DAC 8BIT DUAL V-OUT 20SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS8952-IQZR | 功能描述:以太网 IC IC 100BASE-TX and 10BASE-T Transceiver RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| CS8952T | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:100BASE E-X AND 10BASE-T TRANSCEIVER |

| CS8952T-CQ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:100BASE E-X AND 10BASE-T TRANSCEIVER |

| CS8952T-IQ | 制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:100BASE E-X AND 10BASE-T TRANSCEIVER |

| CS8952T-IQR | 制造商:Cirrus Logic 功能描述:ETHERNET TXRX SGL CHIP 1-PORT 5V 10MBPS/100MBPS 100TQFP - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。