- 您现在的位置:买卖IC网 > PDF目录256924 > CY38015V144-66BBC (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 18.9 ns, PBGA144 PDF资料下载

参数资料

| 型号: | CY38015V144-66BBC |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, 18.9 ns, PBGA144 |

| 封装: | FBGA-144 |

| 文件页数: | 27/32页 |

| 文件大小: | 929K |

| 代理商: | CY38015V144-66BBC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页

PRELIMINARY

Quantum38K ISR

CPLD Family

Document #: 38-03043 Rev. **

Page 4 of 32

General Description

The Quantum38K family, based on a 0.18-

m, 6-layer metal

CMOS logic process, offers a wide range of solutions at very

high system performance. With devices ranging from 256 to

1536 macrocells, Quantum38K is the highest density CPLD in

the market besides Cypress’s Delta39K. Specifically designed

to address low-cost applications, this family also integrates

Cypress’s dual-port memory technology onto a CPLD.

The architecture is based on Logic Block Clusters (LBC) that

are connected by Horizontal and Vertical (H&V) routing chan-

nels. Each LBC features eight individual Logic Blocks (LB).

Adjacent to each LBC is a channel memory block, which can

be accessed directly from the I/O pins. These channel memory

blocks are highly configurable and can be cascaded in width

and depth. See Figure 1 for a block diagram of the

Quantum38K architecture.

All the members of the Quantum38K family have Cypress’s

highly regarded In-System Reprogrammability (ISR) feature,

which simplifies both design and manufacturing flows, thereby

reducing costs. The ISR feature provides the ability to recon-

figure the devices without having design changes cause pi-

nout or timing changes in most cases. The Cypress ISR func-

tion is implemented through a JTAG-compliant serial interface.

Data is shifted in and out through the TDI and TDO pins re-

spectively. Superior routability, simple timing, and the ISR al-

lows users to change existing logic designs while simulta-

neously fixing pinout assignments and maintaining system

performance.

The entire family features JTAG for ISR and boundary scan,

and is compatible with the PCI Local Bus specification, meet-

ing the electrical and timing requirements. The Quantum38K

family also features user programmable bus-hold and slew

rate control capabilities on each I/O pin.

AnyVolt Interface

All Quantum38K devices feature an on-chip regulator, which

accepts 3.3V or 2.5V on the VCC supply pins and steps it down

to 1.8V internally, the voltage level at which the core operates.

With Quantum38K’s AnyVolt technology, the I/O pins can be

connected to either 1.8V 2.5V, or 3.3V. All Quantum38K devic-

es are 3.3V tolerant regardless of VCCIO or VCC settings.

Global Routing Description

The routing architecture of the Quantum38K is made up of

horizontal and vertical (H&V) routing channels. These routing

channels allow signals from each of the Quantum38K archi-

tectural components to communicate with one another. In ad-

dition to the horizontal and vertical routing channels that inter-

connect the I/O banks, channel memory blocks, and logic

block clusters, each LBC contains a Programmable Intercon-

nect Matrix (PIM), which is used to route signals among the

logic blocks.

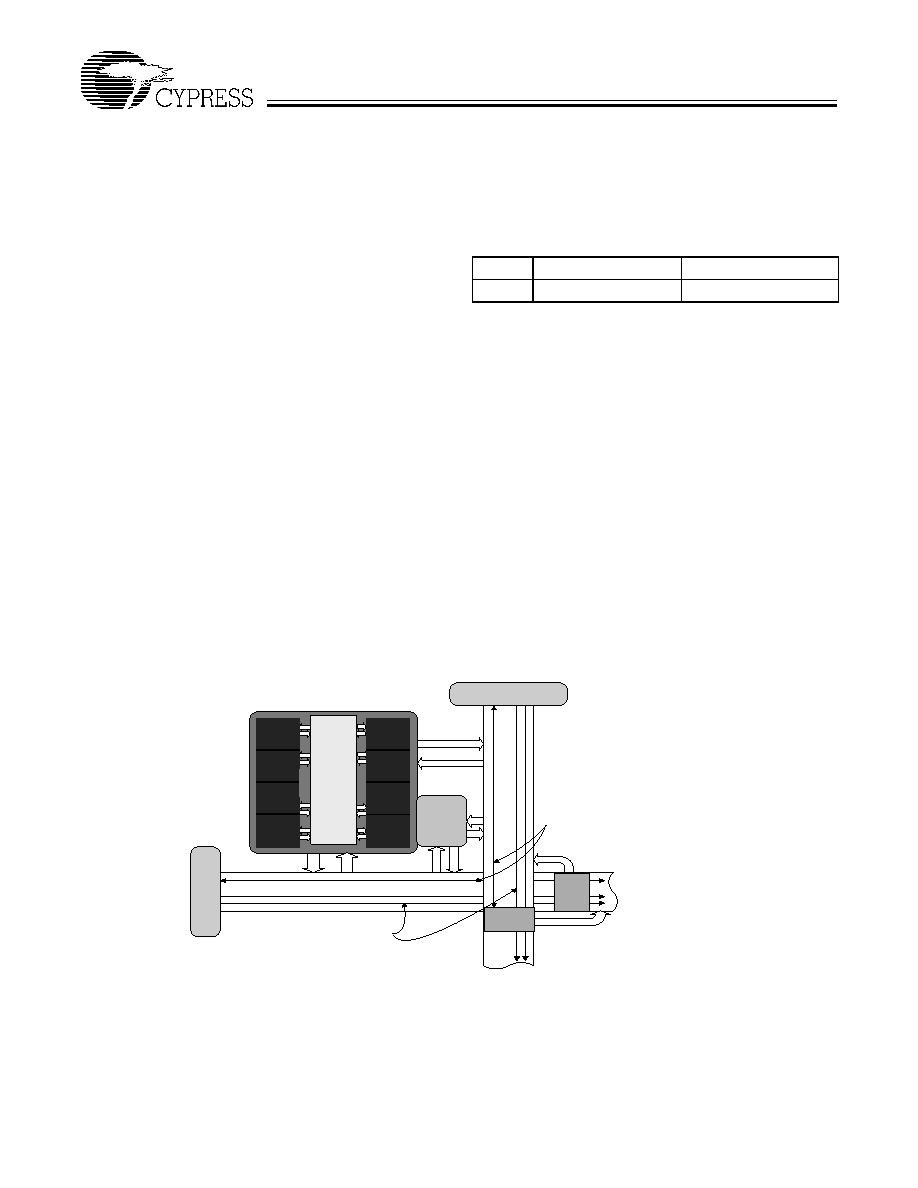

Figure 2 is a block diagram of the routing channels that inter-

face within the Quantum38K architecture. The LBC is exactly

the same for every member of the Quantum38K CPLD family.

Logic Block Cluster (LBC)

The Quantum38K architecture consists of several logic block

clusters, each of which have 8 Logic Blocks (LB) connected

via a Programmable Interconnect Matrix (PIM) as shown in

Figure 3. All LBCs interface with each other via horizontal and

vertical routing channels.

Device

VCC

VCCIO

38K

3.3V or 2.5V

3.3V or 2.5V or 1.8V

Figure 2. Quantum38K Routing Interface

LB

Cluster

PIM

Cluster

Memory

Block

LB

Cluster

Memory

Block

LB

Channel

Memory

Block

I/O Block

I/O

B

lock

Channel memory

outputs drive

dedicated tracks in the

horizontal and vertical

routing channels

H-to-V

PIM

V-to-H

PIM

Pin inputs from the I/O cells

drive dedicated tracks in the

horizontal and vertical routing

channels

72

64

LB

相关PDF资料 |

PDF描述 |

|---|---|

| CY38015V144-66BBI | LOADABLE PLD, 18.9 ns, PBGA144 |

| CY38015V144-83BBC | LOADABLE PLD, 15 ns, PBGA144 |

| CY38015V144-83BBI | LOADABLE PLD, 15 ns, PBGA144 |

| CY38015V208-66NC | LOADABLE PLD, 18.9 ns, PQFP208 |

| CY38015V208-66NI | LOADABLE PLD, 18.9 ns, PQFP208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY38050V208-125NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38050V208-83NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-83NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38100V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 144K GATES 1536 MCRCLLS IND 0.18UM 2.5V/3.3V - Bulk |

发布紧急采购,3分钟左右您将得到回复。