- 您现在的位置:买卖IC网 > PDF目录256924 > CY38015V144-66BBC (CYPRESS SEMICONDUCTOR CORP) LOADABLE PLD, 18.9 ns, PBGA144 PDF资料下载

参数资料

| 型号: | CY38015V144-66BBC |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, 18.9 ns, PBGA144 |

| 封装: | FBGA-144 |

| 文件页数: | 32/32页 |

| 文件大小: | 929K |

| 代理商: | CY38015V144-66BBC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页

PRELIMINARY

Quantum38K ISR

CPLD Family

Document #: 38-03043 Rev. **

Page 9 of 32

I/O Cell

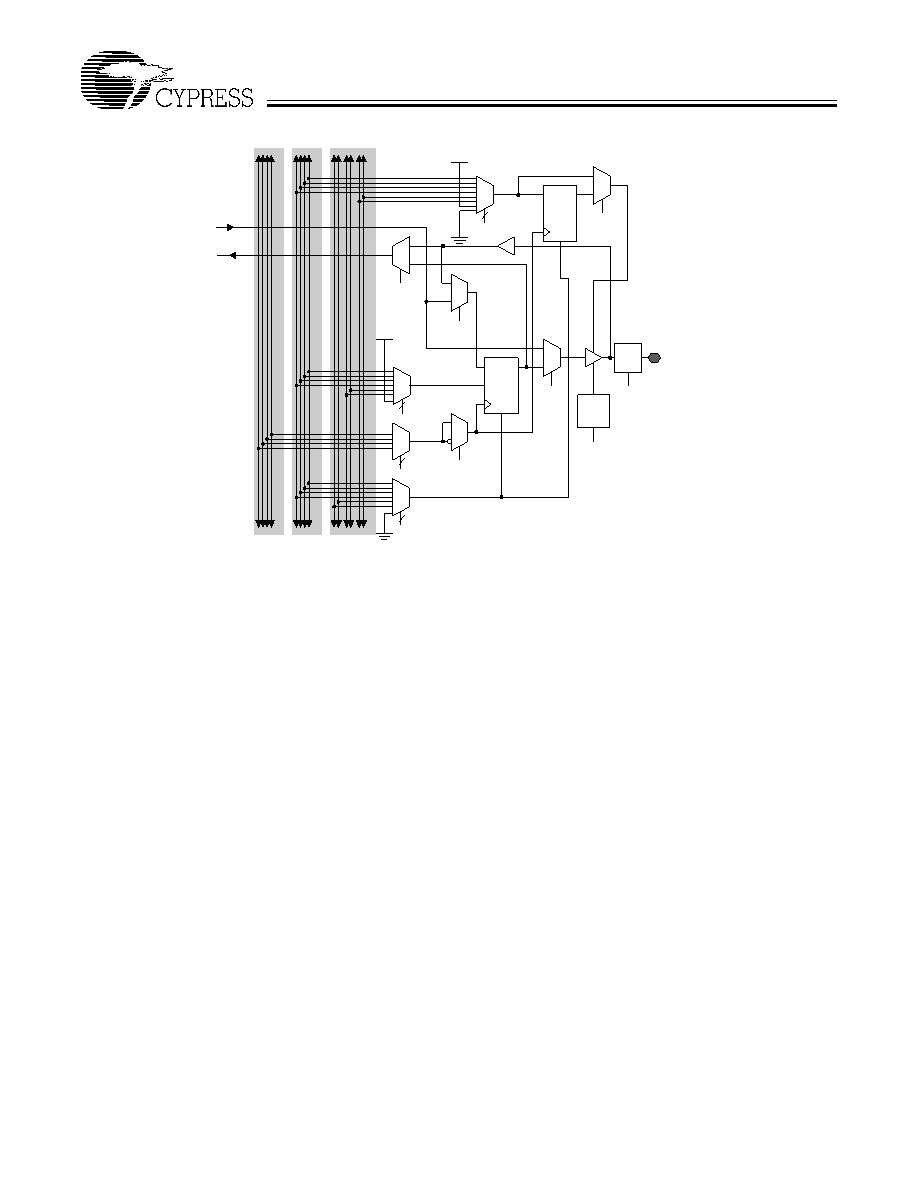

Figure 7 is a block diagram of the Quantum38K I/O cell. The

I/O cell contains a three-state input buffer, an output buffer,

and a register that can be configured as an input or output

register. The output buffer has a slew rate control option that

can be used to configure the output for a slower slew rate. The

input of the device and the pin output can each be configured

as registered or combinatorial; however, only one path can be

configured as registered in a given design.

The output enable can be selected from one of the four global

control signals or from one of two Output Control Channel

(OCC) signals. The output enable can be configured as always

enabled or always disabled or it can be controlled by one of

the remaining inputs to the mux. The selection is done via a

mux that includes VCC and GND as inputs.

One of the global clocks can be selected as the clock for the

I/O cell register. The clock mux output is an input to a clock

polarity mux that allows the input/output register to be clocked

on either edge of the clock.

Slew Rate Control

The ouput buffer has a slew rate control option. This allows the

output buffer to slew at a fast rate (3 V/ns) or a slow rate

(1 V/ns). All I/Os default to fast slew rate. For designs con-

cerned with meeting FCC emissions standards the slow edge

provides for lower system noise. For designs requiring very

high performance the fast edge rate provides maximum sys-

tem performance.

Programmable Bus Hold

On each I/O pin, user-programmable-bus-hold is included.

Bus-hold, which is an improved version of the popular internal

pull-up resistor, is a weak latch connected to the pin that does

not degrade the device’s performance. As a latch, bus-hold

maintains the last state of a pin when the pin is placed in a

high-impedance state, thus reducing system noise in bus-in-

terface applications. Bus-hold additionally allows unused de-

vice pins to remain unconnected on the board, which is partic-

ularly useful during prototyping as designers can route new

signals to the device without cutting trace connections to VCC

or GND. For more information, see the application note “Un-

derstanding Bus-Hold

A Feature of Cypress CPLDs.”

Clocks

Quantum38K has four dedicated clock input pins (GCLK[3:0])

to accept system clocks.

The global clock tree for a Quantum38K device is driven by the

dedicated clock pins, consisting of four global clocks that go to

every macrocell, memory block, and I/O cell.

Clock Tree Distribution

The clock tree distributes the four global clocks to every clus-

ter, channel memory, and I/O block on the die. The global clock

tree is designed such that the clock skew is minimized while

maintaining an acceptable clock delay.

Figure 7. Block Diagram of I/O Cell

DQ

RES

E

G

lobal

C

ontr

o

lSi

gnal

s

O

u

tput

C

ontr

o

lC

hannel

O

C

G

lobal

C

loc

k

Si

gnal

s

Slew

Rate

Control

C

I/O

From

Output PIM

To Routing

Channel

OE Mux

Register Input

Mux

Register Enable

Mux

Output Mux

Clock Mux

Clock

Polarity

Mux

Register Reset

Mux

Input

Mux

Bus

Hold

C

DQ

RES

C

Registered OE

Mux

C

3

C

3

C

2

3

C

相关PDF资料 |

PDF描述 |

|---|---|

| CY38015V144-66BBI | LOADABLE PLD, 18.9 ns, PBGA144 |

| CY38015V144-83BBC | LOADABLE PLD, 15 ns, PBGA144 |

| CY38015V144-83BBI | LOADABLE PLD, 15 ns, PBGA144 |

| CY38015V208-66NC | LOADABLE PLD, 18.9 ns, PQFP208 |

| CY38015V208-66NI | LOADABLE PLD, 18.9 ns, PQFP208 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CY38050V208-125NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38050V208-83NTC | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS COMM 0.18UM 2.5V/3.3V - Bulk |

| CY38050V208-83NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 72K GATES 768 MCRCLLS IND 0.18UM 2.5V/3.3V 2 - Bulk |

| CY38100V208-125NTI | 制造商:Cypress Semiconductor 功能描述:CPLD QUANTUM38K 144K GATES 1536 MCRCLLS IND 0.18UM 2.5V/3.3V - Bulk |

发布紧急采购,3分钟左右您将得到回复。