- 您现在的位置:买卖IC网 > PDF目录17066 > DC746A (Linear Technology)BOARD DELTA SIGMA ADC LTC2412 PDF资料下载

参数资料

| 型号: | DC746A |

| 厂商: | Linear Technology |

| 文件页数: | 17/36页 |

| 文件大小: | 0K |

| 描述: | BOARD DELTA SIGMA ADC LTC2412 |

| 软件下载: | QuikEval System |

| 设计资源: | DC746A Design File DC746A Schematic |

| 标准包装: | 1 |

| 系列: | QuikEval™ |

| ADC 的数量: | 1 |

| 位数: | 24 |

| 采样率(每秒): | 7.5 |

| 数据接口: | MICROWIRE?,串行,SPI? |

| 工作温度: | 0°C ~ 70°C |

| 已用 IC / 零件: | LTC2412 |

| 已供物品: | 板 |

| 相关产品: | DC590B-ND - BOARD DEMO USB SERIAL CONTROLLER LTC2412IGN#PBF-ND - IC ADC 2CH DIFF-IN 24BIT 16SSOP LTC2412IGN#TRPBF-ND - IC ADC 2CH DIFF-IN 24BIT 16SSOP LTC2412CGN#TRPBF-ND - IC ADC 2CH DIFF-IN 24BIT 16SSOP LTC2412CGN#PBF-ND - IC ADC 2CH DIFF-IN 24BIT 16SSOP LTC2412IGN#TR-ND - IC CONV A/D 24B 2CH DIFF 16-SSOP LTC2412CGN#TR-ND - IC CONV A/D 24B 2CH DIFF 16-SSOP LTC2412IGN-ND - IC CONV A/D 24B 2CH DIFF 16-SSOP LTC2412CGN-ND - IC ADC 2CH DIFF-IN 24BIT 16SSOP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

LTC2412

24

2412f

APPLICATIO S I FOR ATIO

WU

U

For a simple approximation, the source impedance RS

driving an analog input pin (IN+, IN–, REF+ or REF–) can be

considered to form, together with RSW and CEQ (see

Figure 11), a first order passive network with a time

constant

τ = (RS + RSW) CEQ. The converter is able to

sample the input signal with better than 1ppm accuracy if

the sampling period is at least 14 times greater than the

input circuit time constant

τ. The sampling process on the

four input analog pins is quasi-independent so each time

constant should be considered by itself and, under worst-

case circumstances, the errors may add.

When using the internal oscillator (FO = LOW or HIGH), the

LTC2412’s front-end switched-capacitor network is clocked

at 76800Hz corresponding to a 13

s sampling period.

Thus, for settling errors of less than 1ppm, the driving

source impedance should be chosen such that

τ≤13s/14

= 920ns. When an external oscillator of frequency fEOSC is

used, the sampling period is 2/fEOSC and, for a settling

error of less than 1ppm,

τ ≤ 0.14/fEOSC.

Input Current

If complete settling occurs on the input, conversion re-

sults will be unaffected by the dynamic input current. An

incomplete settling of the input signal sampling process

may result in gain and offset errors, but it will not degrade

the INL performance of the converter. Figure 11 shows the

mathematical expressions for the average bias currents

flowing through the IN+ and IN– pins as a result of the

sampling charge transfers when integrated over a sub-

stantial time period (longer than 64 internal clock cycles).

The effect of this input dynamic current can be analyzed

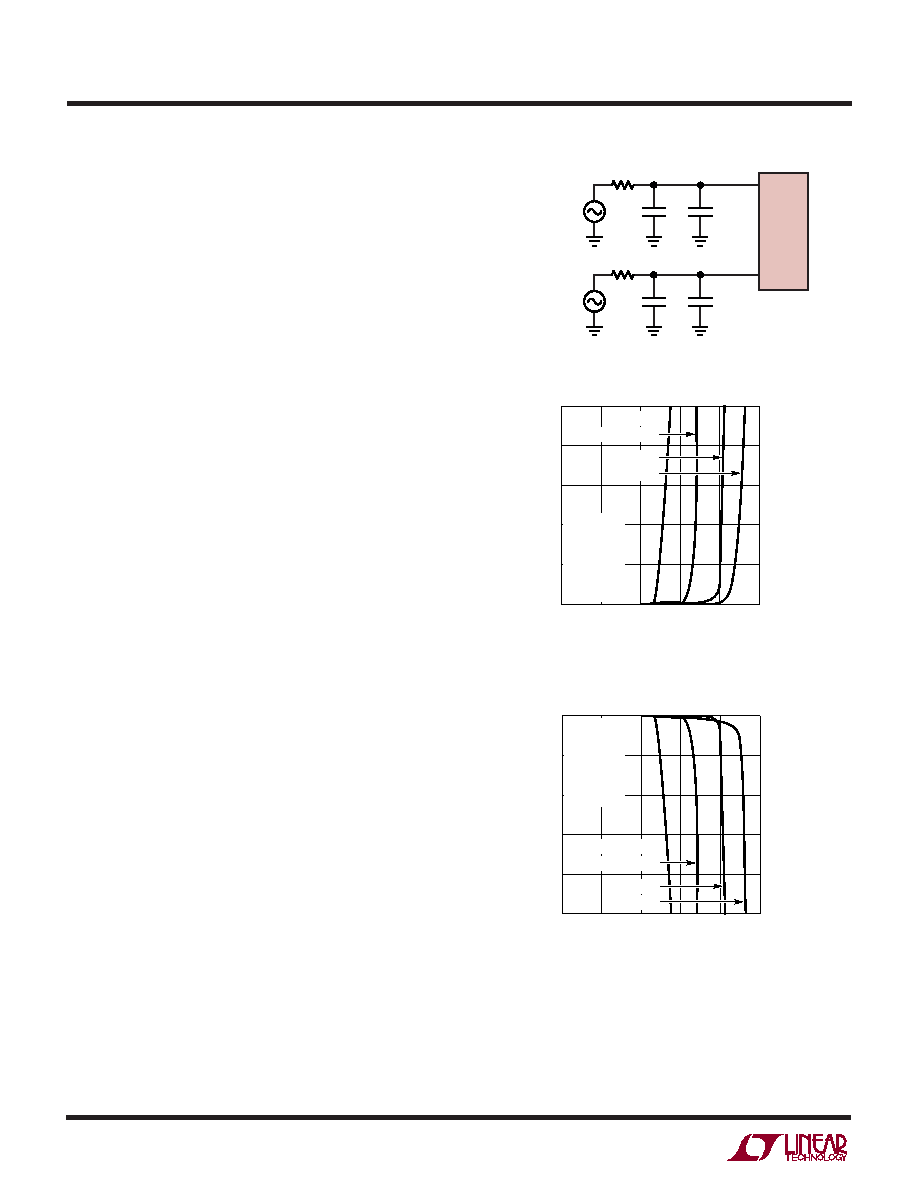

using the test circuit of Figure 12. The CPAR capacitor

includes the LTC2412 pin capacitance (5pF typical) plus

the capacitance of the test fixture used to obtain the results

shown in Figures 13 and 14. A careful implementation can

bring the total input capacitance (CIN + CPAR) closer to 5pF

thus achieving better performance than the one predicted

by Figures 13 and 14. For simplicity, two distinct situa-

tions can be considered.

For relatively small values of input capacitance (CIN <

0.01

F), the voltage on the sampling capacitor settles

almost completely and relatively large values for the

source impedance result in only small errors. Such values

CIN

2412 F12

VINCM + 0.5VIN

RSOURCE

IN+

LTC2412

CPAR

20pF

CIN

VINCM – 0.5VIN

RSOURCE

IN –

CPAR

20pF

Figure 12. An RC Network at IN+ and IN–

Figure 14. –FS Error vs RSOURCE at IN+ or IN– (Small CIN)

Figure 13. +FS Error vs RSOURCE at IN+ or IN– (Small CIN)

RSOURCE ()

1

10

100

1k

10k

100k

+FS

ERROR

(ppm

OF

V

REF

)

2412 F13

50

40

30

20

10

0

VCC = 5V

REF+ = 5V

REF – = GND

IN+ = 5V

IN– = 2.5V

FO = GND

TA = 25°C

CIN = 0.01F

CIN = 0.001F

CIN = 100pF

CIN = 0pF

RSOURCE ()

1

10

100

1k

10k

100k

–

FS

ERROR

(ppm

OF

V

REF

)

2412 F14

0

–10

–20

–30

–40

–50

VCC = 5V

REF+ = 5V

REF – = GND

IN+ = GND

IN– = 2.5V

FO = GND

TA = 25°C

CIN = 0.01F

CIN = 0.001F

CIN = 100pF

CIN = 0pF

for CIN will deteriorate the converter offset and gain

performance without significant benefits of signal filtering

and the user is advised to avoid them. Nevertheless, when

small values of CIN are unavoidably present as parasitics

相关PDF资料 |

PDF描述 |

|---|---|

| SLPX222M100C7P3 | CAP ALUM 2200UF 100V 20% SNAP |

| RS3-243.3DZ/H3 | CONV DC/DC 3W 9-27VIN +/-3.3VOUT |

| AP2162MPG-13 | IC PWR SW USB 2CH 1A 8-MSOP |

| RS3-2415DZ/H3 | CONV DC/DC 3W 9-27VIN +/-15VOUT |

| SC75B-470 | INDUCTOR SMD 47UH 1.10A 2.52MHZ |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DC74HC259 | 制造商:TI 制造商全称:Texas Instruments 功能描述:High Speed CMOS Logic 8-Bit Addressable Latch |

| DC-750 | 制造商:Bivar 功能描述:CARD GUIDE DEEP 7.5" 0.08" BK |

| DC-750-102 | 制造商:Bivar 功能描述:CARD GUIDE DEEP 7.5" 0.102" BK |

| DC-750-102-CI | 制造商:Bivar 功能描述:CARD GUIDE INSERT 7.5" 0.102" BK |

| DC750KA | 制造商:Dewalt 功能描述:9.6V 3/8" Cordless Compact Drill/Driver Kit 制造商:DEWALT 功能描述:9.6V DRILL/DRIVER KIT 3/8 RATCHETING CHUCK |

发布紧急采购,3分钟左右您将得到回复。