- 您现在的位置:买卖IC网 > PDF目录16128 > DMA-MC-O4-N2 (Lattice Semiconductor Corporation)IP CORE MCDMA CTLR ORCA 4 PDF资料下载

参数资料

| 型号: | DMA-MC-O4-N2 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 18/28页 |

| 文件大小: | 0K |

| 描述: | IP CORE MCDMA CTLR ORCA 4 |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | DMAMCO4N2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

�� �

�

Lattice� Semiconductor�

�Multi-Channel� DMA� Controller� User’s� Guide�

�Mode� Register�

�Each� channel� has� a� 6-bit� wide� register.� During� a� write� operation� by� the� microprocessor� when� MCDMA� is� in� idle�

�state,� the� least� two� signi?cant� bits� (bit� 0� and� 1)� of� the� data� bus� determine� which� channel� mode� register� is� being�

�accessed.� A� reset� or� a� master� clear� clears� the� mode� registers.� Table� 7� lists� the� format� of� a� mode� register� in� the�

�8237� mode.�

�Mask� Register�

�This� register� is� only� visible� in� the� 8237� mode.� Each� channel� has� a� bit� associated� with� it� that� is� used� to� mask� a� hard-�

�ware� DMA� request� (disable� the� incoming� dreq� ).� All� four� bits� of� this� register� can� be� accessed� at� once,� or� the� CPU�

�can� program� each� of� the� bits� separately.� Each� mask� bit� is� set� when� its� associated� channel� produces� an� eopout_n�

�signal.� A� reset� or� master� clear� sets� all� four� bits� and� masks� all� the� channels.� Table� 8� and� Table� 9� list� the� mask� regis-�

�ter� format� for� the� 8237� mode.�

�Request� Register�

�This� register� is� only� visible� in� 8237� mode.� The� request� register� allows� software� DMA� requests.� The� values� in� the�

�mask� register� mask� the� hardware� request� (� dreq� ).� Software� requests� generated� from� the� request� register� are� non-�

�maskable.� Individual� bits� of� this� register� can� be� accessed� with� the� channel� number� supplied� on� the� two� least� signif-�

�icant� bits� of� the� data� bus.� A� reset� or� master� clear� clears� this� register.� The� channel� must� be� in� block� mode� in� order� to�

�make� a� software� request.� Table� 10� lists� the� request� register� format� in� 8237� Mode.�

�Status� Register�

�This� register� is� only� available� in� the� 8237� mode.� The� microprocessor� can� read� the� status� register,� which� contains�

�information� about� the� status� of� the� device.� This� information� includes� which� of� the� channels� have� completed� their�

�DMA� service� and� which� channels� have� a� DMA� request� pending.� The� Status� Register� is� reset� upon� a� hardware�

�reset� or� a� master� clear.� Bits� 0� through� 3,� which� indicate� which� channel� has� reached� Terminal� Count,� are� cleared�

�every� time� the� Status� register� is� read.� Bits� 4� through� 7� are� set� when� their� corresponding� channel� is� requesting� ser-�

�vice.� Table� 11� shows� the� status� register� format.�

�Temporary� Register�

�This� register� holds� data� during� memory-to-memory� transfers.� A� reset� or� master� clear� command� clears� this� register.�

�The� microprocessor� can� read� this� register� in� the� 8237� mode� while� the� MCDMA� is� in� the� idle� state.� This� register�

�yields� the� last� data� transferred� during� the� most� recent� memory-to-memory� transfer.�

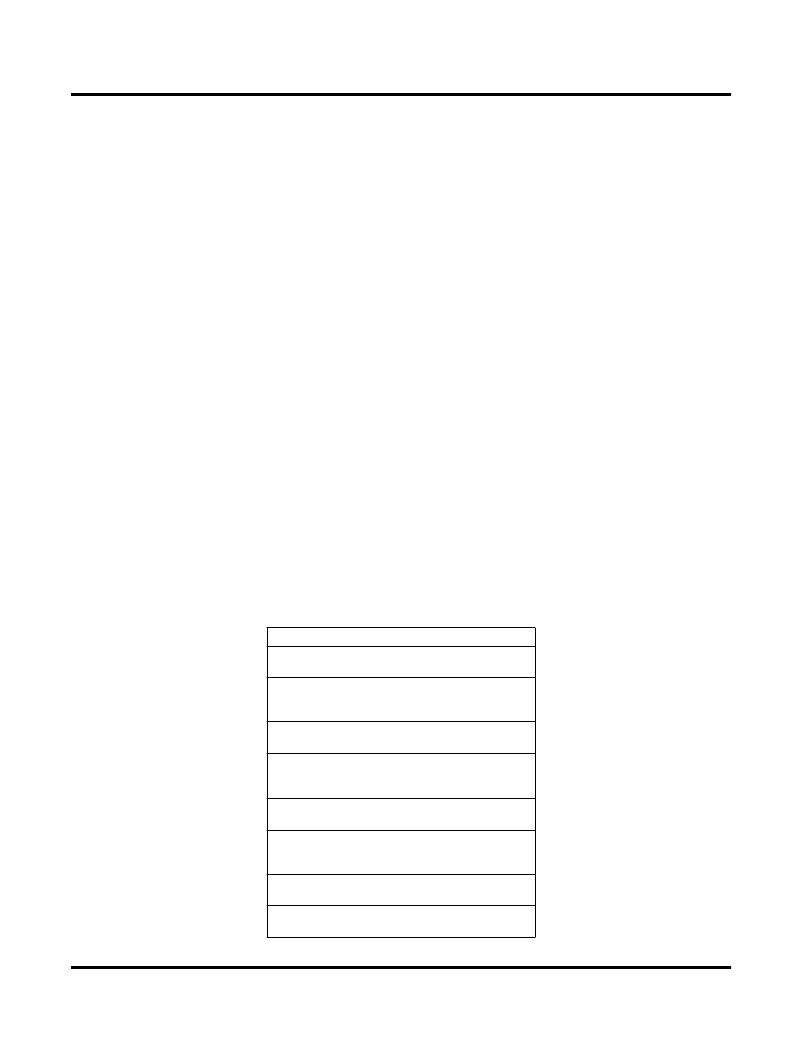

�Table� 6.� Command� Register� -� 8237� Mode�

�Bit�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�X�

�X�

�X�

�Description�

�Memory-to-memory� disable�

�Memory-to-memory� enable�

�Channel� 0� address� hold� disable�

�Channel� 0� address� hold� enable�

�if� bit0� =� 0�

�Controller� enable�

�Controller� disable�

�Normal� timing�

�Compressed� timing�

�if� bit0� =� 1�

�Fixed� Priority�

�Rotating� Priority�

�Late� Write�

�Extended� Write�

�if� bit3� =� 1�

�dreq� active� high�

�dreg� active� low�

�dack� active� low�

�dack� active� high�

�18�

�相关PDF资料 |

PDF描述 |

|---|---|

| LHL10TB220K | INDUCTOR 22UH 2.1A RADIAL |

| EBC31DRTH | CONN EDGECARD 62POS DIP .100 SLD |

| LHL10TB183J | INDUCTOR 18000UH 81MA RADIAL |

| LHL10TB182J | INDUCTOR 1800UH .29A RADIAL |

| 1487EK | WIREWAY BOX CONNECTOR 8X8" |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DMA-MC-SC-N3 | 功能描述:数字信号处理器和控制器 - DSP, DSC DMA Controller RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| DMA-MC-XM-N3 | 功能描述:数字信号处理器和控制器 - DSP, DSC DMA Controller RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| DMA-MC-XP-N2 | 功能描述:数字信号处理器和控制器 - DSP, DSC DMA Controller RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| DM-A-PP | 制造商:DDK 制造商全称:DDK Ltd. 功能描述:Conversion Connector |

| DMA-SG-E3-U1 | 功能描述:开发软件 DMA Scatter/Gather RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

发布紧急采购,3分钟左右您将得到回复。