- 您现在的位置:买卖IC网 > PDF目录1211 > DMA-MC-XP-N2 (Lattice Semiconductor Corporation)IP CORE MCDMA CTLR XPGA ISPXPGA PDF资料下载

参数资料

| 型号: | DMA-MC-XP-N2 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 13/28页 |

| 文件大小: | 0K |

| 描述: | IP CORE MCDMA CTLR XPGA ISPXPGA |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | DMAMCXPN2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

�� �

�

Lattice� Semiconductor�

�Multi-Channel� DMA� Controller� User’s� Guide�

�Signal� Descriptions�

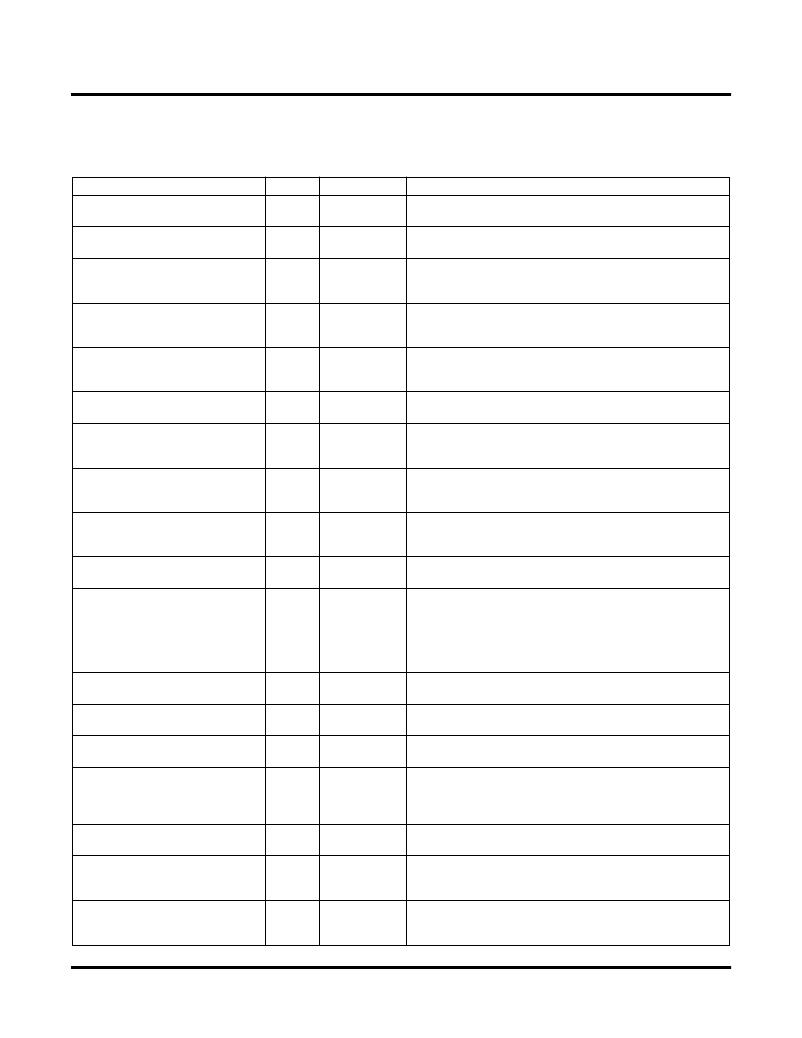

�Table� shows� the� input� and� output� ports� of� the� MCDMA� core� that� apply� for� both� 8237� and� non-8237� modes.�

�Table� 4.� Signal� De?nitions� of� the� MCDMA� Controller�

�clk�

�Port� Name�

�Type�

�Input�

�Active� State�

�Rising� Edge�

�Description�

�Clock� .� This� signal� controls� and� synchronizes� the� operations�

�of� the� MCDMA.�

�cs_n�

�Input�

�Low�

�Chip� Select� .� This� is� an� active� low� signal� used� to� select� the�

�MCDMA.�

�reset�

�Input�

�High�

�Reset� .� This� is� an� active� high� signal� that� clears� the� internal�

�registers.� After� reset,� the� device� is� placed� in� the� Idle� state�

�and� the� DMA� requests� are� masked.�

�ready�

�Input�

�High�

�Ready� .� This� is� an� active� high� signal� used� to� extend� the� mem-�

�ory� read� and� write� pulses� from� the� MCDMA.� This� is� most� of�

�often� used� to� accommodate� slow� memories.�

�hlda�

�Input�

�High�

�Hold� Acknowledge� .� This� active� high� signal� generated� by� the�

�CPU� indicates� the� CPU� has� relinquished� control� of� the� sys-�

�tem� buses.�

�eopin_n�

�Input�

�Low�

�End� Of� Process� Input� .� This� active� low� input� permits� the�

�external� termination� of� the� current� DMA� service.�

�iorin_n�

�Input�

�Low�

�I/O� Read� Inpu� t.� This� is� an� active� low� signal� when� asserted�

�along� with� cs_n� .� Thus,� it� permits� the� CPU� to� read� the� internal�

�registers� of� MCDMA.�

�iowin_n�

�Input�

�Low�

�I/O� Write� Input� .� This� is� an� active� low� signal.� When� asserted�

�along� with� cs_n� ,� it� permits� the� CPU� to� write� into� the� internal�

�registers� of� the� MCDMA.�

�ain� [AIN_BUS_WIDTH-1:0]�

�Input�

�N/A�

�Address� .� This� signal� selects� one� of� the� internal� registers.� In�

�the� 8237� mode,� ain� is� 4� bits� wide.� In� the� non-8237� mode,� the�

�bus� width� depends� on� the� number� of� channels� selected.�

�dbin� [DATA_BUS_WIDTH-1:0]�

�Input�

�N/A�

�Data� Bus� Input� .� The� CPU� writes� to� the� internal� registers�

�through� this� data� bus.�

�dreq[N-1:0]�

�Input�

�High/Low�

�(8237)�

�High�

�(Non-8237)�

�DMA� Request� .� These� programmable� parity� signals� are� asyn-�

�chronous� signals� generated� by� peripherals� requesting� DMA�

�service.� A� device� reset� initializes� dreq� to� active� high.�

�In� 8237� mode,� these� parity� signals� are� programmable� to� be�

�active� high� or� low.� In� non-8237,� these� signals� are� always�

�active� high.�

�hreq�

�Output�

�High�

�Hold� Request� .� This� is� an� active� high� signal� sent� to� the� CPU�

�to� request� control� over� the� system� bus.�

�eopout_n�

�Output�

�Low�

�End� of� Process� Out� .� This� active� low� signal� indicates� normal�

�termination� of� a� DMA� service.�

�iorout_n�

�Output�

�Low�

�I/O� Read� Output� .� This� active� low� signal� is� used� to� access�

�data� from� a� peripheral� during� a� DMA� Write� transfer.�

�dbout� [DATA_BUS_WIDTH-1:0]�

�Output�

�N/A�

�Data� Bus� Output� .� This� bus� contains� the� value� of� the� internal�

�register� when� read� by� the� CPU.� In� the� write-to-memory�

�phase� of� the� memory-to-memory� DMA� operation,� the� dbout�

�data� bus� transmits� the� data� from� the� temporary� register.�

�iowout_n�

�Output�

�Low�

�I/O� Write� Output� .� This� active� low� signal� is� used� to� load� data�

�to� a� peripheral� during� a� DMA� Read� transfer.�

�memw_n�

�Output�

�Low�

�Memory� Write� .� This� active� low� signal� is� used� to� indicate� that�

�data� is� being� written� to� the� selected� memory� location� during� a�

�DMA� Write� or� a� memory-to-memory� transfer.�

�memr_n�

�Output�

�Low�

�Memory� Read� .� This� active� low� signal� is� used� to� indicate� that�

�data� is� being� read� from� the� selected� memory� location� during�

�a� DMA� Read� or� a� memory-to-memory� transfer.�

�13�

�相关PDF资料 |

PDF描述 |

|---|---|

| DN-5002C | N-WAY ETHERNET SWITCH 8-PORT |

| DN-7006GS | WIRELESS LAN PCI ADAPTER |

| DN-7020 | WIFI FINDER W/DISPLAY WLAN ADAPT |

| DN-93501-U/BL | CONN JCK RJ45 TOOL FREE CAT5E BK |

| DN-93501-U/B | CONN JCK RJ45 TOOL FREE CAT5E BU |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DM-A-PP | 制造商:DDK 制造商全称:DDK Ltd. 功能描述:Conversion Connector |

| DMA-SG-E3-U1 | 功能描述:开发软件 DMA Scatter/Gather RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| DMA-SG-E3-UT1 | 功能描述:开发软件 DMA SCATTER/GATHER USER CONFIGURABLE RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| DMA-SG-P2-U1 | 功能描述:开发软件 DMA Scatter/Gather RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| DMA-SG-P2-UT1 | 功能描述:开发软件 DMA SCATTER/GATHER RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

发布紧急采购,3分钟左右您将得到回复。