- 您现在的位置:买卖IC网 > PDF目录1914 > DS2153Q-A7+T&R (Maxim Integrated Products)IC TXRX E1 1-CHIP 5V 44-PLCC PDF资料下载

参数资料

| 型号: | DS2153Q-A7+T&R |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 37/60页 |

| 文件大小: | 0K |

| 描述: | IC TXRX E1 1-CHIP 5V 44-PLCC |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 500 |

| 功能: | 单芯片收发器 |

| 接口: | E1 |

| 电路数: | 1 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 电流 - 电源: | 65mA |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LCC(J 形引线) |

| 供应商设备封装: | 44-PLCC(16.59x16.59) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

DS2153Q

42 of 60

13.3 Jitter Attenuator

The DS2153Q contains an on-board jitter attenuator that can be set to a depth of either 32 or 128 bits via

the JABDS bit in the Line Interface Control Register (LICR). The 128-bit mode is used in applications

where large excursions of wander are expected. The 32-bit mode is used in delay sensitive applications.

The characteristics of the attenuation are shown in Figure 13-4. The jitter attenuator can be placed in

either the receive path or the transmit path by appropriately setting or clearing the JAS bit in the LICR.

Also, the jitter attenuator can be disabled (in effect, removed) by setting the DJA bit in the LICR. In order

for the jitter attenuator to operate properly, a crystal with the specifications listed in Table 13-4 must be

connected to the XTAL1 and XTAL2 pins.

The jitter attenuator divides the clock provided by the 8.192MHz crystal at the XTAL1 and XTAL2 pins

to create an output clock that contains very little jitter. On-board circuitry will pull the crystal (by

switching in or out load capacitance) to keep it long-term averaged to the same frequency as the incoming

E1 signal. If the incoming jitter exceeds either 120UIP-P (buffer depth is 128 bits) or 28UIP-P (buffer depth

is 32 bits), then the DS2153Q will divide the attached crystal by either 3.5 or 4.5 instead of the normal 4

to keep the buffer from overflowing. When the device divides by either 3.5 or 4.5, it also sets the Jitter

Attenuator Limit Trip (JALT) bit in the Receive Information Register (RIR.5).

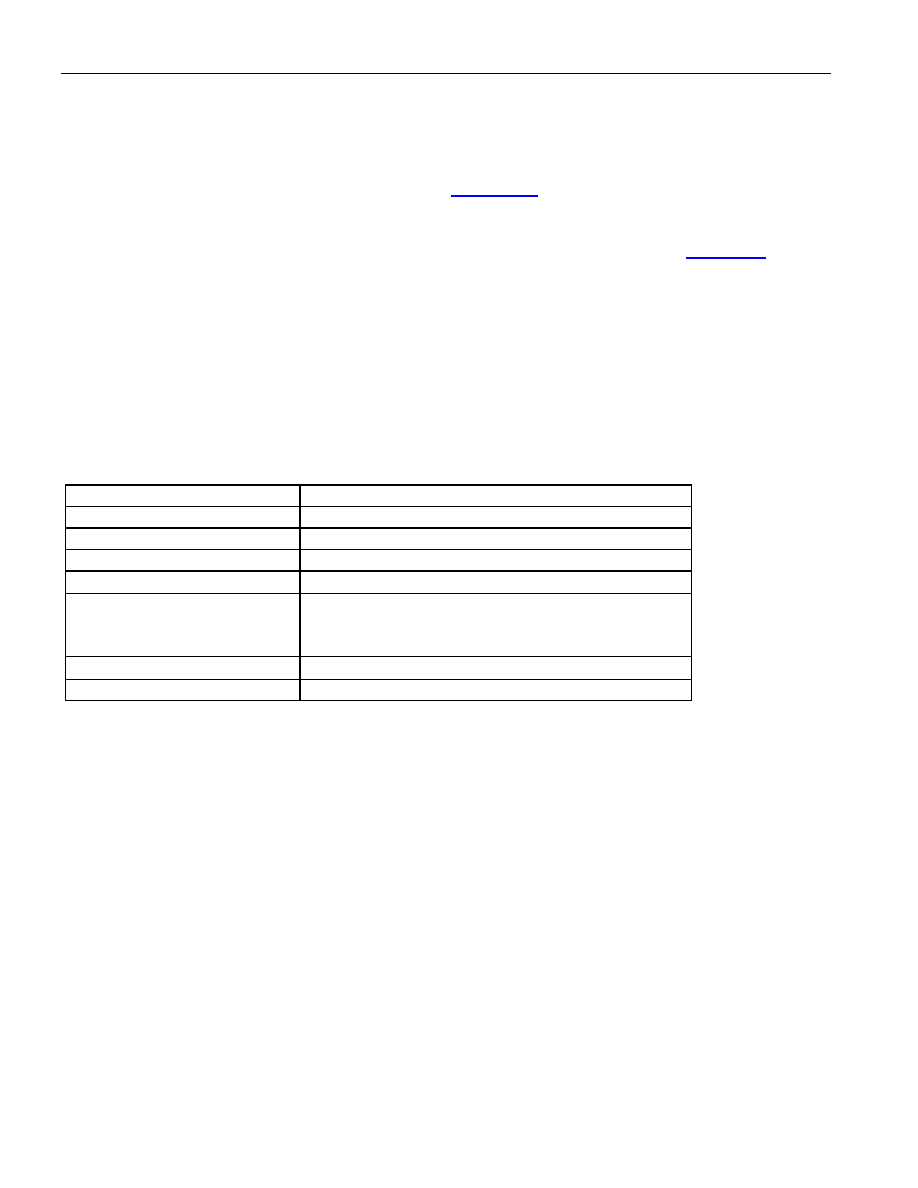

Table 13-4. Crystal Selection Guidelines

PARAMETER

SPECIFICATION

Parallel Resonant Frequency

8.192MHz

Mode

Fundamental

Load Capacitance

18pF to 20pF (18.5pF nominal)

Tolerance

±50ppm

Pullability

CL = 10pF, delta frequency = +175ppm to

+250ppm

CL = 45pF, delta frequency = -175ppm to -250ppm

Effective Series Resistance

30

maximum

Crystal Cut

AT

相关PDF资料 |

PDF描述 |

|---|---|

| DS2154LNA2+ | IC TXRX E1 5V 100-LQFP |

| DS2154L | IC TXRX E1 1CHIP 5V ENH 100-LQFP |

| DS2155LN | IC TXRX T1/E1/J1 1-CHIP 100-LQFP |

| DS2156LN+ | IC TXRX T1/E1/J1 1-CHIP 100-LQFP |

| DS2172T/T&R | IC TESTER BIT ERROR RATE 32-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS2153QN | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM Transceiver |

| DS2153QN-A5 | 功能描述:IC TXRX E1 1-CHIP 5V IND 44-PLCC RoHS:否 类别:集成电路 (IC) >> 接口 - 电信 系列:- 产品培训模块:Lead (SnPb) Finish for COTS 产品变化通告:Product Discontinuation 06/Feb/2012 标准包装:750 系列:* |

| DS2153QN-A7 | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS2153QN-A7/T&R | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

| DS2153QN-A7/T&R+ | 制造商:Maxim Integrated Products 功能描述:FRAMER E1/ISDN-PRI/PCM-30 5V 44PLCC - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。