- 您现在的位置:买卖IC网 > PDF目录97909 > EM6617SO24A 30V N-Channel PowerTrench MOSFET PDF资料下载

参数资料

| 型号: | EM6617SO24A |

| 元件分类: | MOSFETs |

| 英文描述: | 30V N-Channel PowerTrench MOSFET |

| 中文描述: | 30V的N沟道的PowerTrench MOSFET的 |

| 文件页数: | 6/67页 |

| 文件大小: | 824K |

| 代理商: | EM6617SO24A |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页

EM6617

03/02 REV. C/442

Copyright

2002, EM Microelectronic-Marin SA

14

www.emmicroelectronic.com

7.2 Port A

The EM6617 has one four bit general purpose CMOS input port. The port A input can be read at any time,

internal pull-up or pull-down resistors can be chosen. All selections concerning port A are bit-wise executable.

I.e. Pull-up on PA[2], pull-down on PA[0], positive IRQ edge on PA[0] but negative on PA[1], etc.

In sleep mode the port A pull-up or pull-down resistors are turned off, and the inputs are deactivated except if

the InpResSleep bit in the option register OPTFSelPB is set to 1. In this case the port A inputs are continuously

monitored to match the input reset condition which will immediately wake the EM6617 from sleep mode (all pull

resistors remain).

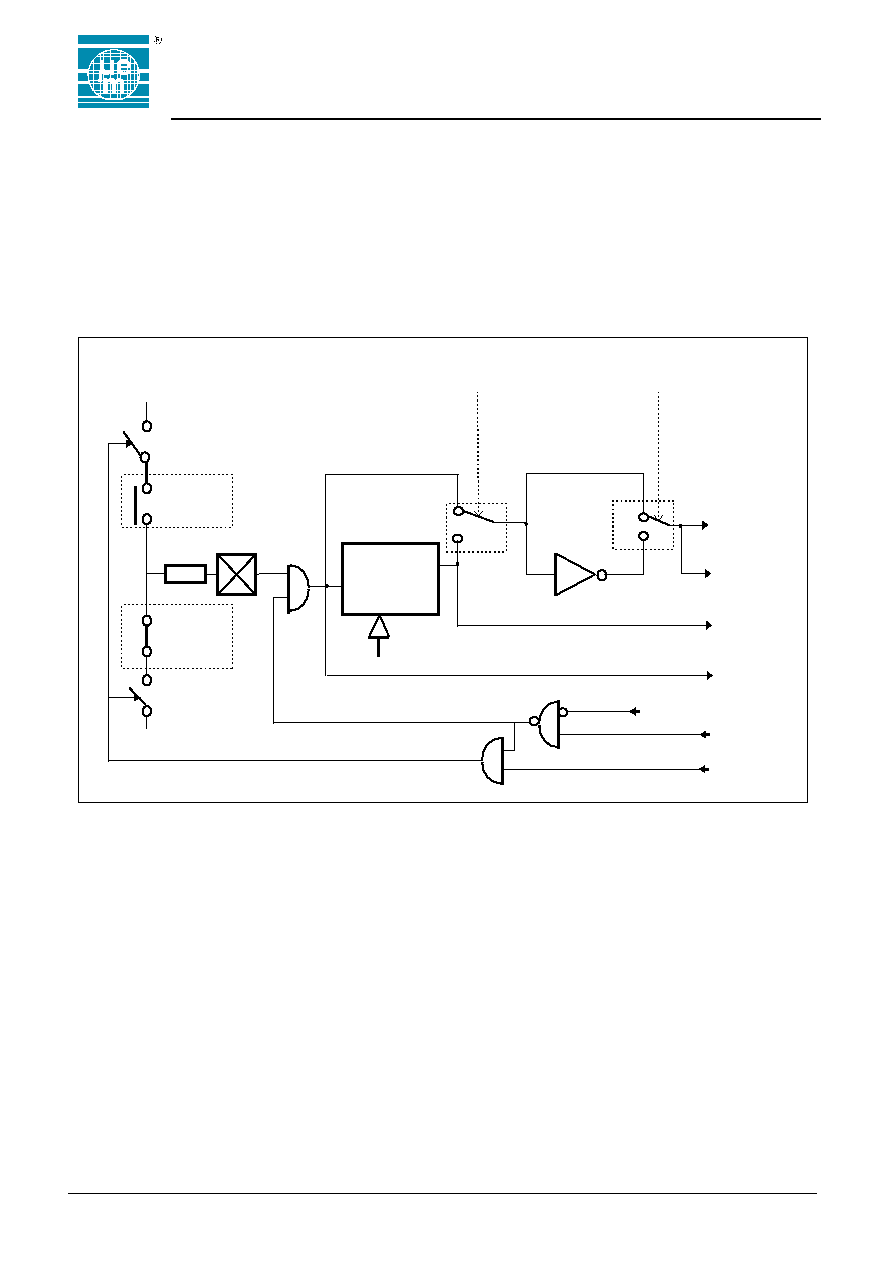

Figure 12. Input Port A Configuration

IntEdgPA[n]=0

NoDebIntPA[n]=1

Mask opt

MPAPU[n]

IRQPA[3:0]

PA[n]terminal

PA0, PA3

for 10-Bit

Counter

Mask opt

MPAPD[n]

Debouncer

P TestVar

Ck[8]

Ck[11] or

Ck[14]

DB[3:0]

NoPullPA[n]

Vbat

(VDD)

VSS

Input Reset allowed

when in Sleep

Sleep

7.2.1 IRQ on Port A

For interrupt request generation (IRQ) one can choose direct or debouncer input and positive or negative edge

IRQ triggering. With the debouncer selected ( OPTDebIntPA ) the input must be stable for two rising edges of

the selected debouncer clock (RegPresc). This means a worst case of 16 ms (default) or 2 ms (0.25 ms by

metal mask) with a system clock of 32 KHz.

Either a positive or a negative edge on the port A inputs - after debouncer or not - can generate an interrupt

request. This selection is done in the option register OPTIntEdgPA.

All four bits of port A can provide an IRQ, each pin with its own interrupt mask bit in the RegIRQMask1 register.

When an IRQ occurs, inspection of the RegIRQ1, RegIRQ2 and RegIRQ3 registers allows the interrupt to be

identified and treated.

At power on or after any reset the RegIRQMask1 is set to 0, thus disabling any input interrupt. A new interrupt is

only stored with the next active edge after the corresponding interrupt mask is cleared. See also the interrupt

chapter 13.

It is recommended to mask the port A IRQ’s while one changes the selected IRQ edge. Else one may generate

a IRQ (Software IRQ). I.e. PA[0] on ‘0’ then changing from positive to negative edge selection on PA[0] will

immediately trigger an IRQPA[0] if the IRQ was not masked.

相关PDF资料 |

PDF描述 |

|---|---|

| EM6617SO24B | 30V N-Channel PowerTrench MOSFET |

| EM6617SO28A | Advanced Synchronous Rectified Buck MOSFET Drivers with Pre-POR OVP; Temperature Range: 0°C to 70°C; Package: 8-EPSOIC T&R |

| EM6617SO28B | Advanced Synchronous Rectified Buck MOSFET Drivers with Pre-POR OVP; Temperature Range: -40°C to 85°C; Package: 8-EPSOIC T&R |

| EM6617TP28A | Advanced Synchronous Rectified Buck MOSFET Drivers with Pre-POR OVP; Temperature Range: 0°C to 70°C; Package: 8-EPSOIC T&R |

| EM6617TP28B | Advanced Synchronous Rectified Buck MOSFET Drivers with Pre-POR OVP; Temperature Range: -40°C to 85°C; Package: 8-EPSOIC T&R |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EM6617SO24B | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microcontroller |

| EM6617SO28A | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microcontroller |

| EM6617SO28B | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microcontroller |

| EM6617TP28A | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microcontroller |

| EM6617TP28B | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Microcontroller |

发布紧急采购,3分钟左右您将得到回复。