- 您现在的位置:买卖IC网 > PDF目录299030 > EP20K100BC484-2 (ALTERA CORP) LOADABLE PLD, PBGA484 PDF资料下载

参数资料

| 型号: | EP20K100BC484-2 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA484 |

| 文件页数: | 28/68页 |

| 文件大小: | 975K |

| 代理商: | EP20K100BC484-2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

34

4317K–AVR–03/2013

AT90PWM2/3/2B/3B

This clock may be selected as the system clock by programming the CKSEL Fuses as shown in

Table 7-6. If selected, it will operate with no external components. During reset, hardware loads

the pre-programmed calibration value into the OSCCAL Register and thereby automatically cal-

ibrates the RC Oscillator. The accuracy of this calibration is shown as Factory calibration in

By changing the OSCCAL register from SW, see “Oscillator Calibration Register – OSCCAL” on

page 34, it is possible to get a higher calibration accuracy than by using the factory calibration.

The accuracy of this calibration is shown as User calibration in Table 26-1 on page 303.

When this Oscillator is used as the chip clock, the Watchdog Oscillator will still be used for the

Watchdog Timer and for the Reset Time-out. For more information on the pre-programmed cali-

bration value, see the section “Calibration Byte” on page 284.

Notes:

1. The device is shipped with this option selected.

2. If 8 MHz frequency exceeds the specification of the device (depends on VCC), the CKDIV8

Fuse can be programmed in order to divide the internal frequency by 8.

When this Oscillator is selected, start-up times are determined by the SUT Fuses as shown in

Note:

1. If the RSTDISBL fuse is programmed, this start-up time will be increased to

14CK + 4.1 ms to ensure programming mode can be entered.

2. The device is shipped with this option selected.

Table 7-8.

Oscillator Calibration Register – OSCCAL

Bits 7..0 – CAL7..0: Oscillator Calibration Value

The Oscillator Calibration Register is used to trim the Calibrated Internal RC Oscillator to

remove process variations from the oscillator frequency. The factory-calibrated value is automat-

ically written to this register during chip reset, giving an oscillator frequency of 8.0 MHz at 25°C.

The application software can write this register to change the oscillator frequency. The oscillator

can be calibrated to any frequency in the range 7.3 - 8.1 MHz within ±1% accuracy. Calibration

outside that range is not guaranteed.

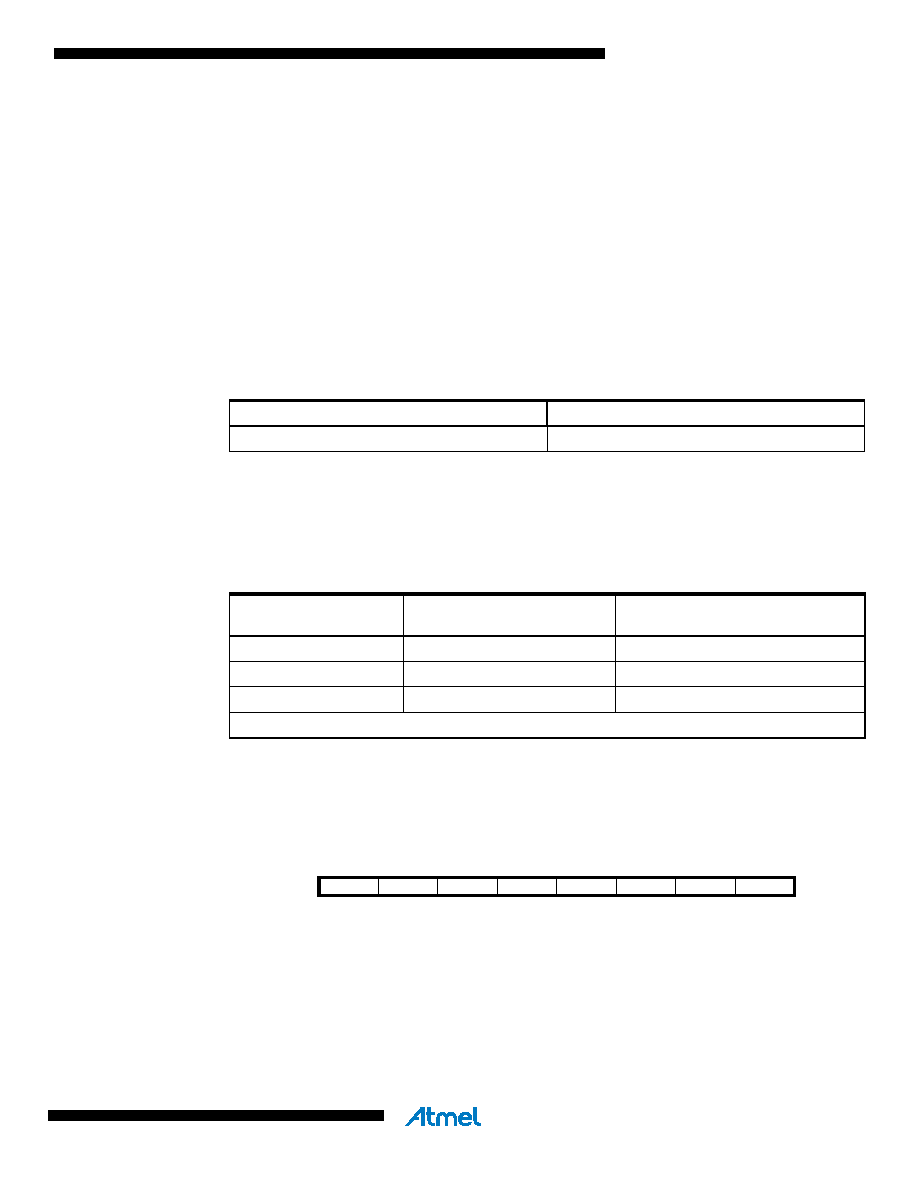

Table 7-6.

Internal Calibrated RC Oscillator Operating Modes(1)(2)

Frequency Range (MHz)

CKSEL3..0

7.3 - 8.1

0010

Table 7-7.

Start-up times for the internal calibrated RC Oscillator clock selection

Power Conditions

Start-up Time from Power-

down and Power-save

Additional Delay from

Reset (V

CC = 5.0V)

SUT1..0

BOD enabled

6 CK

14CK(1)

00

Fast rising power

6 CK

14CK + 4.1 ms

01

Slowly rising power

6 CK

14CK + 65 ms(1)

10

Reserved

11

Bit

76543210

CAL7

CAL6

CAL5

CAL4

CAL3

CAL2

CAL1

CAL0

OSCCAL

Read/Write

R/W

Initial Value

Device Specific Calibration Value

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100BC484-3 | LOADABLE PLD, PBGA484 |

| EP20K100BI484-1 | LOADABLE PLD, PBGA484 |

| EP20K100BI484-2 | LOADABLE PLD, PBGA484 |

| EP20K100BI484-3 | LOADABLE PLD, PBGA484 |

| EP20K100BC672-1 | LOADABLE PLD, PBGA672 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K100BI356-1 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| EP20K100BI356-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100BI356-2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| EP20K100BI356-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100BI356-3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

发布紧急采购,3分钟左右您将得到回复。