- 您现在的位置:买卖IC网 > PDF目录299030 > EP20K100BC484-2 (ALTERA CORP) LOADABLE PLD, PBGA484 PDF资料下载

参数资料

| 型号: | EP20K100BC484-2 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA484 |

| 文件页数: | 68/68页 |

| 文件大小: | 975K |

| 代理商: | EP20K100BC484-2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页当前第68页

Altera Corporation

9

Preliminary Information

APEX 20K Programmable Logic Device Family Data Sheet

MegaLAB Structure

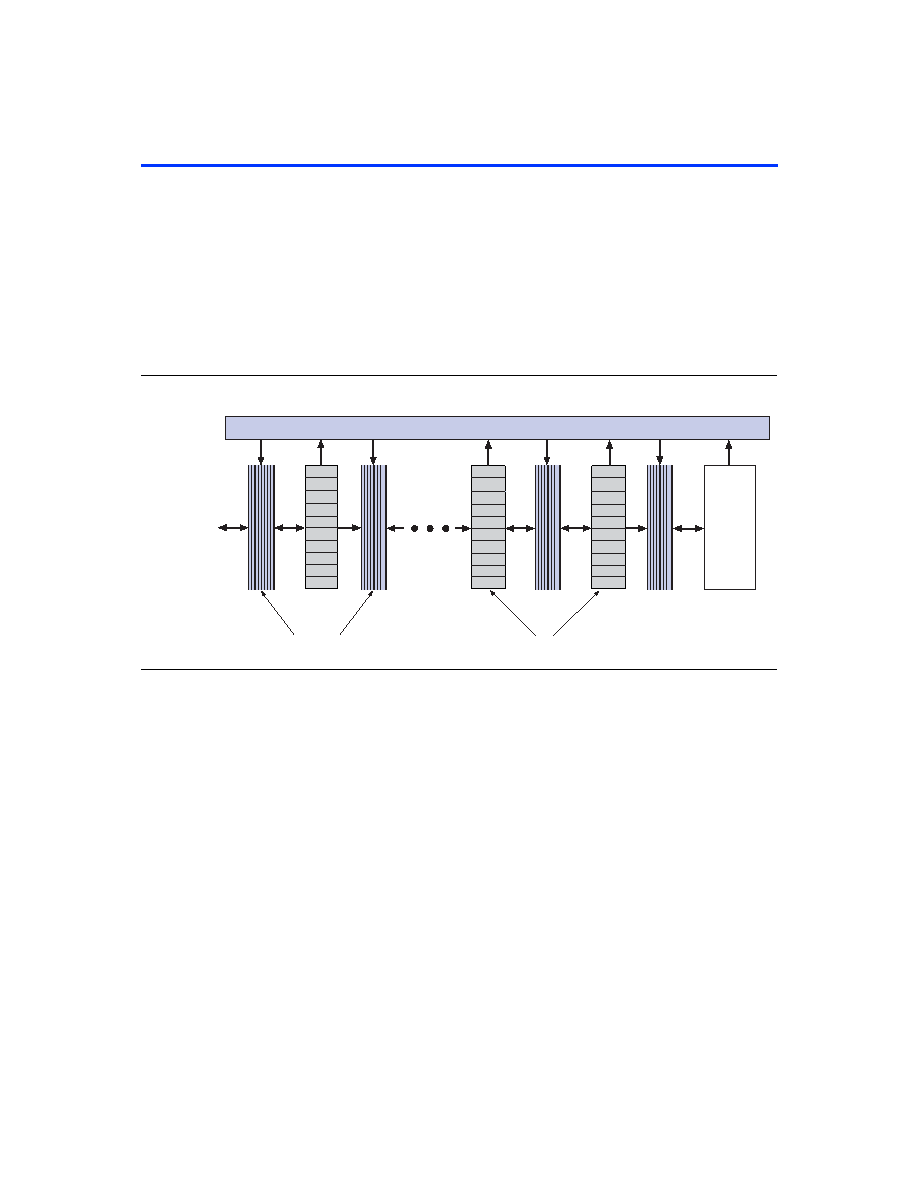

APEX 20K devices are constructed from a series of MegaLAB structures.

Each MegaLAB structure contains 16 logic array blocks (LABs), one ESB,

and a MegaLAB interconnect, which routes signals within the MegaLAB

structure. In the EP10K1000E and EP10K1500E device, MegaLAB

structures contain 24 LABs. Signals are routed between MegaLAB

structures and I/O pins via the FastTrack Interconnect. In addition, edge

LABs can drive I/O pins through the local interconnect. Figure 2 shows

the MegaLAB structure.

Figure 2. MegaLAB Structure

Logic Array Block

Each LAB consists of 10 LEs, the LEs’ associated carry and cascade chains,

LAB control signals, and the local interconnect. The local interconnect

transfers signals between LEs in the same or adjacent LABs, IOEs, or ESBs.

The Quartus Compiler places associated logic within an LAB or adjacent

LABs, allowing the use of a fast local interconnect for high performance.

Figure 3 shows the APEX 20K LAB.

APEX 20K devices use an interleaved LAB structure. This structure allows

each LE to drive two local interconnect areas. This feature minimizes use

of the MegaLAB and FastTrack interconnect, providing higher

performance and flexibility. Each LE can drive 29 other LEs through the

fast local interconnect.

ESB

MegaLAB Interconnect

Local

Interconnect

To Adjacent

LAB or IOEs

LABs

LE1

LE2

LE3

LE4

LE5

LE6

LE7

LE8

LE9

LE10

LE1

LE2

LE3

LE4

LE5

LE6

LE7

LE8

LE9

LE10

LE1

LE2

LE3

LE4

LE5

LE6

LE7

LE8

LE9

LE10

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100BC484-3 | LOADABLE PLD, PBGA484 |

| EP20K100BI484-1 | LOADABLE PLD, PBGA484 |

| EP20K100BI484-2 | LOADABLE PLD, PBGA484 |

| EP20K100BI484-3 | LOADABLE PLD, PBGA484 |

| EP20K100BC672-1 | LOADABLE PLD, PBGA672 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K100BI356-1 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| EP20K100BI356-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100BI356-2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| EP20K100BI356-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100BI356-3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

发布紧急采购,3分钟左右您将得到回复。