- 您现在的位置:买卖IC网 > PDF目录299031 > EP20K100EFI784-1 (ALTERA CORP) LOADABLE PLD, PBGA784 PDF资料下载

参数资料

| 型号: | EP20K100EFI784-1 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA784 |

| 文件页数: | 1/65页 |

| 文件大小: | 781K |

| 代理商: | EP20K100EFI784-1 |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页

Altera Corporation

23

APEX 20K

Programmable Logic

Device Family

May 1999, ver. 2

Data Sheet

A-DS-APEX20K-02

Features...

s

Industry’s first programmable logic device (PLD) incorporating

System-on-a-Programmable-ChipTM integration

–

MultiCoreTM architecture integrating look-up table (LUT) logic,

product-term logic, and embedded memory

–

Embedded system block (ESB) implementation of product-term

logic used for combinatorial-intensive functions

Preliminary

Information

–

LUT logic used for register-intensive functions

–

ESB used to implement memory functions, including first-in

first-out (FIFO) buffers, dual-port RAM, and content-

addressable memory (CAM)

s

High density

–

100,000 to 1 million typical gates (see Table 1)

–

Up to 42,240 logic elements (LEs)

–

Up to 540,672 RAM bits that can be used without reducing

available logic

–

Up to 4,224 product-term-based macrocells

Notes:

(1)

The embedded IEEE Std. 1149.1 JTAG boundary-scan circuitry contributes up to 52,130 additional gates.

(2)

This information is preliminary.

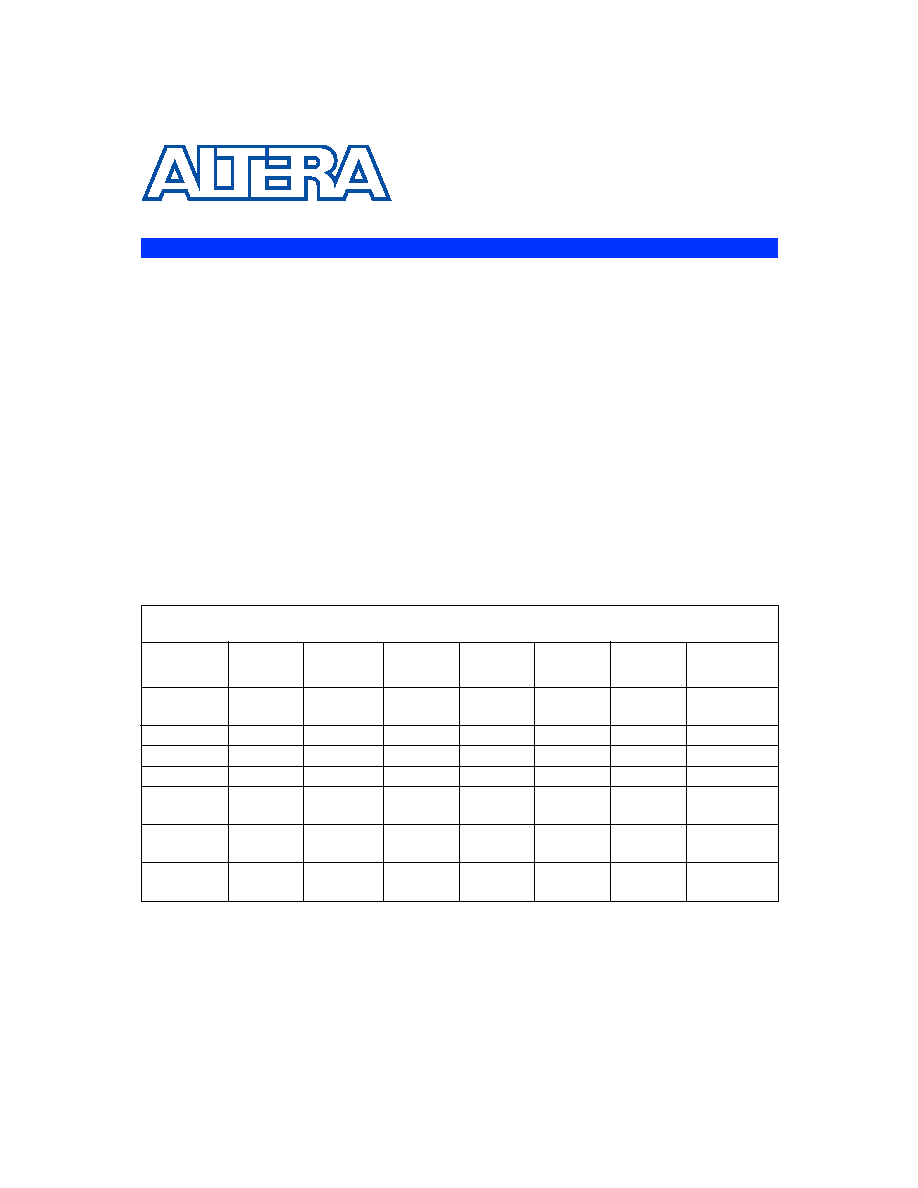

Table 1. APEX 20K Device Features

Feature

EP20K100E

EP20K100

EP20K160E EP20K200E

EP20K200

EP20K300E EP20K400E

EP20K400

EP20K600E EP20K1000E

Maximum

system gates

263,000

404,000

526,000

728,000

1,052,000

1,537,000

2,670,000

Typical gates

106,000

163,000

211,000

293,000

423,000

618,000

1,073,000

LEs

4,160

6,400

8,320

11,520

16,640

24,320

42,240

ESBs

26

40

52

72

104

152

264

Maximum

RAM bits

53,248

81,920

106,496

147,456

212,992

311,296

540,672

Maximum

macrocells

416

640

832

1,152

1,664

2,432

4,224

Maximum

user I/O pins

252

320

382

420

502

620

780

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100EFI784-2 | LOADABLE PLD, PBGA784 |

| EP20K100EFI784-3 | LOADABLE PLD, PBGA784 |

| EP20K200BC784-1 | LOADABLE PLD, PBGA784 |

| EP20K200BC784-2 | LOADABLE PLD, PBGA784 |

| EP20K200BC784-3 | LOADABLE PLD, PBGA784 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K100EQC208-1 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 151 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100EQC208-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100EQC208-1X | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 151 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100EQC208-2 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 151 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100EQC208-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。