- 您现在的位置:买卖IC网 > PDF目录299031 > EP20K100EFI784-1 (ALTERA CORP) LOADABLE PLD, PBGA784 PDF资料下载

参数资料

| 型号: | EP20K100EFI784-1 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA784 |

| 文件页数: | 23/65页 |

| 文件大小: | 781K |

| 代理商: | EP20K100EFI784-1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页

Altera Corporation

25

Preliminary Information

APEX 20K Programmable Logic Device Family Data Sheet

s

Advanced interconnect structure

–

Four-level hierarchical FastTrack Interconnect structure

providing fast, predictable interconnect delays

–

Dedicated carry chain that implements arithmetic functions such

as fast adders, counters, and comparators (automatically used by

software tools and megafunctions)

–

Dedicated cascade chain that implements high-speed,

high-fan-in logic functions (automatically used by software tools

and megafunctions)

–

Interleaved local interconnect allows one LE to drive 29 other

LEs through the fast local interconnect

s

Advanced packaging options

–

Available in a variety of packages with 144 to 984 pins (see

–

FineLine BGATM packages maximize board space efficiency

–

SameFrameTM pin migration providing migration capability

across device densities and package sizes

s

Advanced software support

–

Software design support and automatic place-and-route

provided by the Altera QuartusTM development system for

Windows-based PCs, Sun SPARCstations, and HP 9000

Series 700/800 workstations

–

Altera MegaCoreTM functions and Altera Megafunction Partners

Program (AMPPSM) megafunctions

–

NativeLinkTM integration with popular synthesis, simulation,

and timing analysis tools

–

Quartus SignalTapTM embedded logic analyzer simplifying

in-system design evaluation by giving access to internal nodes

during device operation

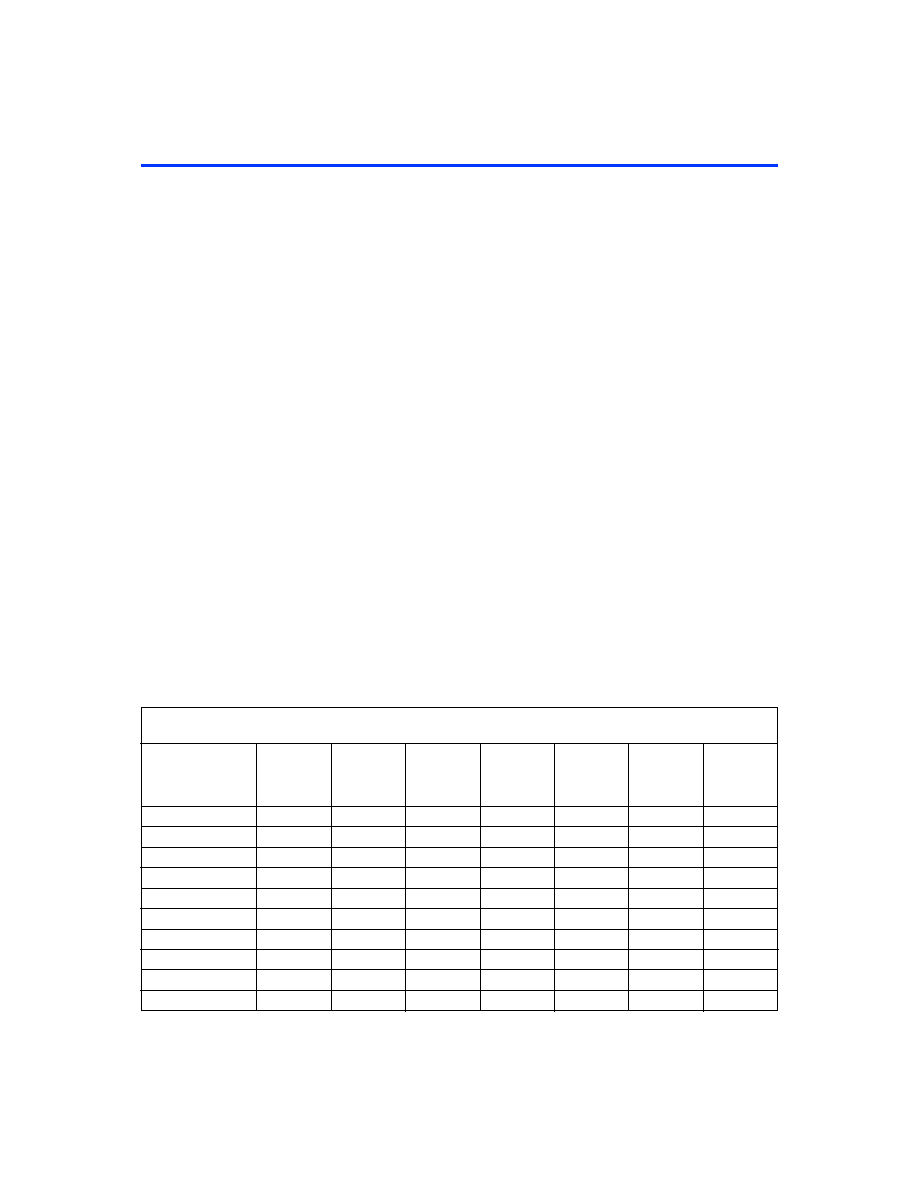

Table 3. APEX 20K QFP, BGA & PGA Package Options & I/O Count

Device

144-Pin

TQFP

208-Pin

PQFP

RQFP

240-Pin

PQFP

RQFP

356-Pin

BGA

652-Pin

BGA

655-Pin

PGA

984-Pin

PGA

EP20K100

101

159

189

252

EP20K100E

92

149

181

v

EP20K160E

84

141

173

v

EP20K200

144

174

v

EP20K200E

134

166

v

EP20K300E

118

150

v

EP20K400

502

EP20K400E

100

132

v

EP20K600E

v

EP20K1000E

v

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100EFI784-2 | LOADABLE PLD, PBGA784 |

| EP20K100EFI784-3 | LOADABLE PLD, PBGA784 |

| EP20K200BC784-1 | LOADABLE PLD, PBGA784 |

| EP20K200BC784-2 | LOADABLE PLD, PBGA784 |

| EP20K200BC784-3 | LOADABLE PLD, PBGA784 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K100EQC208-1 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 151 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100EQC208-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100EQC208-1X | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 151 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100EQC208-2 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 151 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100EQC208-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。