- 您现在的位置:买卖IC网 > PDF目录17030 > EVAL-AD7730LEBZ (Analog Devices Inc)BOARD EVALUATION FOR AD7730 PDF资料下载

参数资料

| 型号: | EVAL-AD7730LEBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 26/53页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD7730 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 24 |

| 采样率(每秒): | 600 |

| 数据接口: | 串行 |

| 输入范围: | ±80 mV |

| 在以下条件下的电源(标准): | 125mW @ 600SPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD7730 |

| 已供物品: | 板,CD |

| 相关产品: | AD7730LBRUZ-ND - IC ADC TRANSDUCER BRIDGE 24TSSOP AD7730LBRZ-ND - IC ADC TRANSDUCER BRIDGE 24SOIC AD7730LBRUZ-REEL7-ND - IC ADC TRANSDUCER BRIDGE 24TSSOP AD7730LBRZ-REEL-ND - IC ADC TRANSDUCER BRIDGE 24SOIC AD7730LBRUZ-REEL-ND - IC ADC TRANSDUCER BRIDGE 24TSSOP AD7730BRUZ-REEL7-ND - IC ADC BRIDGE TRANSDUCER 24TSSOP AD7730BRUZ-REEL-ND - IC ADC BRIDGE TRANSDUCER 24TSSOP AD7730BRUZ-ND - IC ADC TRANSDUCER BRIDGE 24TSSOP AD7730BNZ-ND - IC ADC TRANSDUCER BRIDGE 24-DIP AD7730BRZ-REEL7TR-ND - IC ADC BRDGE TRANSDCR 24SOIC TR 更多... |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页

AD7730/AD7730L

–32–

The range of input span in both the unipolar and bipolar modes

has a minimum value of 0.8

× FS and a maximum value of

2.1

× FS. However, the span (which is the difference between

the bottom of the AD7730’s input range and the top of its input

range) has to take into account the limitation on the positive

full-scale voltage. The amount of offset which can be accommo-

dated depends on whether the unipolar or bipolar mode is being

used. Once again, the offset has to take into account the limita-

tion on the positive full-scale voltage. In unipolar mode, there is

considerable flexibility in handling negative (with respect to

AIN(–)) offsets. In both unipolar and bipolar modes, the range

of positive offsets that can be handled by the part depends on

the selected span. Therefore, in determining the limits for sys-

tem zero-scale and full-scale calibrations, the user has to ensure

that the offset range plus the span range does exceed 1.05

× FS.

This is best illustrated by looking at a few examples.

If the part is used in unipolar mode with a required span of

0.8

× FS, the offset range the system calibration can handle is

from –1.05

× FS to +0.25 × FS. If the part is used in unipolar

mode with a required span of FS, the offset range the system cali-

bration can handle is from –1.05

× FS to +0.05 × FS. Similarly, if

the part is used in unipolar mode and required to remove an

offset of 0.2

× FS, the span range the system calibration can

handle is 0.85

× FS.

If the part is used in bipolar mode with a required span of

±0.4 × FS, the offset range the system calibration can handle is

from –0.65

× FS to +0.65 × FS. If the part is used in bipolar

mode with a required span of

±FS, the offset range the system

calibration can handle is from –0.05

× FS to +0.05 × FS. Simi-

larly, if the part is used in bipolar mode and required to remove

an offset of

±0.2 × FS, the span range the system calibration can

handle is

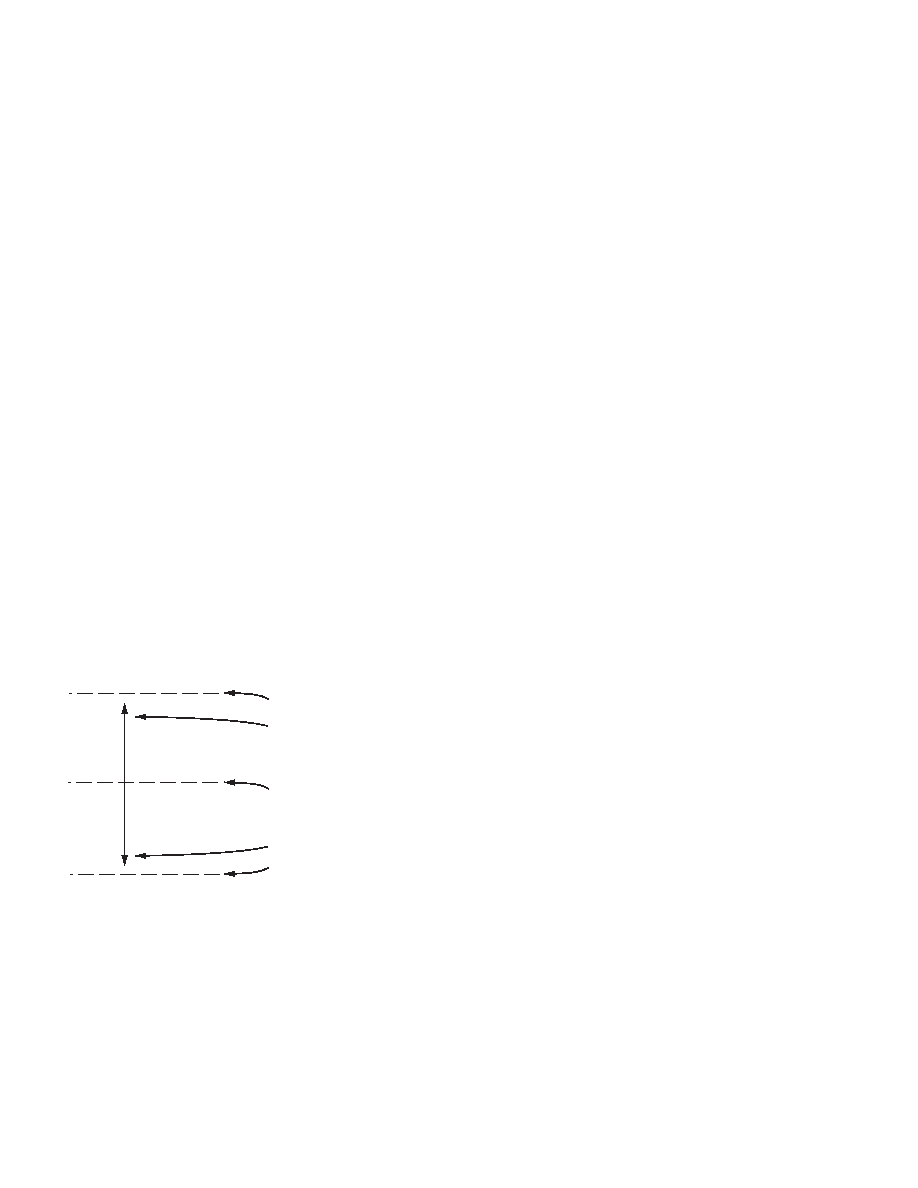

±0.85 × FS. Figure 16 summarizes the span and offset

ranges.

UPPER LIMIT. AD7730’s INPUT

VOLTAGE CANNOT EXCEED THIS

0V DIFFERENTIAL

1.05

FS.

NOMINAL ZERO-SCALE POINT

–1.05

FS.

LOWER LIMIT. AD7730’s INPUT

VOLTAGE CANNOT EXCEED THIS

AD7730

INPUT RANGE

(0.8

FS TO

2.1

FS)

GAIN CALIBRATIONS EXPAND OR

CONTRACT THE AD7730’s INPUT

RANGE

ZERO-SCALE CALIBRATIONS

MOVE INPUT RANGE UP OR DOWN

Figure 16. Span and Offset Limits

Power-Up and Calibration

On power-up, the AD7730 performs an internal reset which sets

the contents of the internal registers to a known state. There are

default values loaded to all registers after a power-on or reset.

The default values contain nominal calibration coefficients for

the calibration registers. To ensure correct calibration for the

device, a calibration routine should be performed after power-up.

The power dissipation and temperature drift of the AD7730 are

low and no warm-up time is required before the initial calibra-

tion is performed. If, however, an external reference is being

used, this reference must have stabilized before calibration is

initiated. Similarly, if the clock source for the part is generated

from a crystal or resonator across the MCLK pins, the start-up

time for the oscillator circuit should elapse before a calibration

is initiated on the part (see below).

Drift Considerations

The AD7730 uses chopper stabilization techniques to minimize

input offset drift. Charge injection in the analog multiplexer and

dc leakage currents at the analog input are the primary sources

of offset voltage drift in the part. The dc input leakage current is

essentially independent of the selected gain. Gain drift within

the converter depends primarily upon the temperature tracking

of the internal capacitors. It is not affected by leakage currents.

When operating the part in CHOP mode (CHP = 1), the signal

chain including the first-stage filter is chopped. This chopping

reduces the overall offset drift to 5 nV/

°C. Integral and differen-

tial linearity errors are not significantly affected by temperature

changes.

Care must also be taken with external drift effects in order to

achieve optimum drift performance. The user has to be espe-

cially careful to avoid, as much as possible, thermocouple effects

from junctions of different materials. Devices should not be

placed in sockets when evaluating temperature drift, there

should be no links in series with the analog inputs and care

must be taken as to how the input voltage is applied to the input

pins. The true offset drift of the AD7730 itself can be evaluated

by performing temperature drift testing of the part with the

AIN(–)/AIN(–) input channel arrangement (i.e., internal shorted

input, test mode).

USING THE AD7730

Clocking and Oscillator Circuit

The AD7730 requires a master clock input, which may be an

external CMOS compatible clock signal applied to the MCLK IN

pin with the MCLK OUT pin left unconnected. Alternatively, a

crystal or ceramic resonator of the correct frequency can be

connected between MCLK IN and MCLK OUT in which case

the clock circuit will function as an oscillator, providing the

clock source for the part. The input sampling frequency, the

modulator sampling frequency, the –3 dB frequency, output

update rate and calibration time are all directly related to the

master clock frequency, fCLK IN. Reducing the master clock

frequency by a factor of two will halve the above frequencies and

update rate and double the calibration time.

The crystal or ceramic resonator is connected across the MCLK

IN and MCLK OUT pins, as per Figure 17. Capacitors C1 and

C2 may or may not be required and may vary in value depend-

ing on the crystal/resonator manufacturer's recommendations.

The AD7730 has a capacitance of 5 pF on MCLK IN and 13 pF

on MCLK OUT so, in most cases, capacitors C1 and C2 will

not be required to get the crystal/resonator operating at its cor-

rect frequency.

REV. B

相关PDF资料 |

PDF描述 |

|---|---|

| EBC20DRTN-S93 | CONN EDGECARD 40POS DIP .100 SLD |

| RGM06DTKN-S288 | CONN EDGECARD 12POS .156 EXTEND |

| EBC20DRTH-S93 | CONN EDGECARD 40POS DIP .100 SLD |

| PCMC133E-1R0MF | COIL 1.0 UH POWER CHOKE 20% SMD |

| RYM06DTKH-S288 | CONN EDGECARD 12POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7731EB | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk |

| EVAL-AD7731EBZ | 功能描述:BOARD EVALUATION FOR AD7731 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7732EB | 制造商:Analog Devices 功能描述:2-CHANNEL, ??10 V INPUT RANGE, HIGH THROUGHPUT, 24-BIT ADC |

| EVAL-AD7732EBZ | 功能描述:BOARD EVAL FOR AD7732 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7734EBZ | 功能描述:BOARD EVALUATION FOR AD7734 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

发布紧急采购,3分钟左右您将得到回复。