- 您现在的位置:买卖IC网 > PDF目录17050 > EVAL-AD7763EDZ (Analog Devices Inc)BOARD EVAL CONTROL AD7763 PDF资料下载

参数资料

| 型号: | EVAL-AD7763EDZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 1/33页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL CONTROL AD7763 |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 24 |

| 采样率(每秒): | 625k |

| 数据接口: | 并联 |

| 输入范围: | ±3.25 Vpp |

| 在以下条件下的电源(标准): | 955.5mW @ 625kSPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD7763 |

| 已供物品: | 板,CD |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页

24-Bit, 625 kSPS, 109 dB Sigma-Delta

ADC with On-Chip Buffers, Serial Interface

Data Sheet

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibilityis assumedbyAnalogDevicesforitsuse,norforanyinfringementsof patentsorother

rightsofthirdpartiesthatmayresultfromitsuse.Specificationssubjecttochangewithoutnotice.No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

2005–2014 Analog Devices, Inc. All rights reserved.

FEATURES

120 dB dynamic range at 78 kHz output data rate

109 dB dynamic range at 625 kHz output data rate

112 dB SNR at 78 kHz output data rate

107 dB SNR at 625 kHz output data rate

625 kHz maximum fully filtered output word rate

Programmable oversampling rate (32× to 256×)

Flexible serial interface

Fully differential modulator input

On-chip differential amplifier for signal buffering

Low-pass finite impulse response (FIR) filter with default

or user-programmable coefficients

Overrange alert bit

Digital offset and gain correction registers

Low power and power-down modes

Synchronization of multiple devices via SYNC pin

I2S interface mode

APPLICATIONS

Data acquisition systems

Vibration analysis

Instrumentation

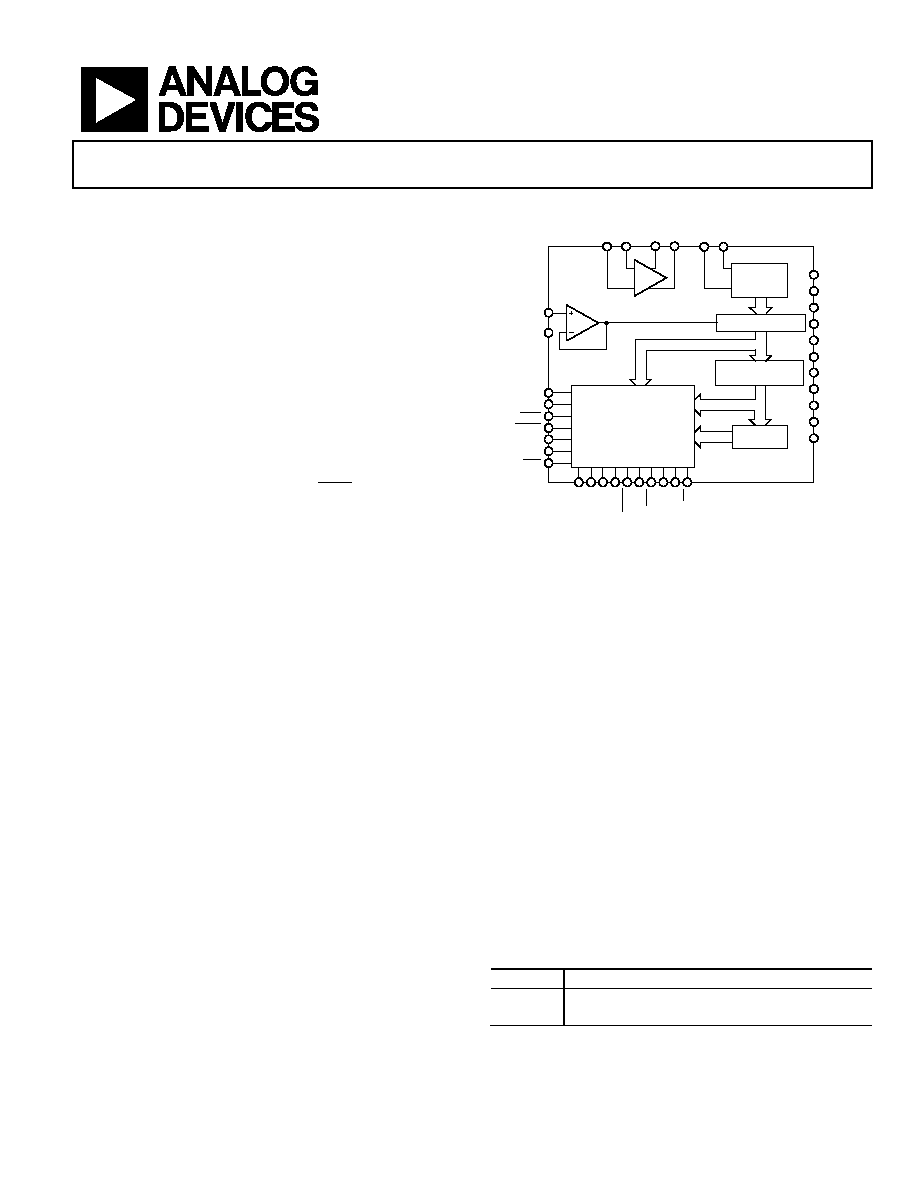

FUNCTIONAL BLOCK DIAGRAM

05476-

00

1

AD7763

VIN+

VIN–

AVDD1

AGND

MCLK

DGND

VDRIVE

AVDD2

AVDD3

AVDD4

DVDD

DECAPA

RBIAS

DECAPB

MCLKGND

SYNC

RESET

SH2:0

ADR2:0

CDIV

I2

S

SC

P

SC

R

SDL

DRD

Y

SC

O

FSO

SD

O

SD

I

FS

I

CONTROL LOGIC

I/O

OFFSET AND GAIN

REGISTERS

DIFF

MULTIBIT

-

MODULATOR

RECONSTRUCTION

VREF+

REFGND

FIR FILTER

ENGINE

PROGRAMMABLE

DECIMATION

BUF

Figure 1.

GENERAL DESCRIPTION

The AD7763 high performance, 24-bit, Σ-Δ analog-to-digital

converter (ADC) combines wide input bandwidth and high

speed with the benefits of Σ-Δ conversion, as well as performance

of 107 dB SNR at 625 kSPS, making it ideal for high speed data

acquisition. A wide dynamic range, combined with significantly

reduced antialiasing requirements, simplifies the design process.

An integrated buffer to drive the reference, a differential ampli-

fier for signal buffering and level shifting, an overrange flag,

internal gain and offset registers, and a low-pass, digital FIR

filter make the AD7763 a compact, highly integrated data

acquisition device requiring minimal peripheral component

selection. In addition, the device offers programmable

decimation rates and a digital FIR filter, which can be user-

programmed to ensure that its characteristics are tailored for the

user’s application. The AD7763 is ideal for applications demanding

high SNR without necessitating the design of complex, front-

end signal processing.

The differential input is sampled at up to 40 MSPS by an analog

modulator. The modulator output is processed by a series of

low-pass filters, the final filter having default or user-programmable

coefficients. The sample rate, filter corner frequencies, and

output word rate are set by a combination of the external clock

frequency and the configuration registers of the AD7763.

The reference voltage supplied to the AD7763 determines the

analog input range. With a 4 V reference, the analog input range

is ±3.2 V differential-biased around a common mode of 2 V.

This common-mode biasing can be achieved using the on-chip

differential amplifiers, further reducing the external signal

conditioning requirements.

The AD7763 is available in an exposed paddle, 64-lead TQFP_EP

and is specified over the industrial temperature range from

40°C to +85°C.

Table 1. Related Devices

Part No.

Description

24-bit, 2.5 MSPS, 100 dB Σ-Δ, parallel interface

24-bit, 625 kSPS, 109 dB Σ-Δ, parallel interface

相关PDF资料 |

PDF描述 |

|---|---|

| EVAL-AD7401AEDZ | BOARD EVAL FOR AD7401 |

| HI5860SOICEVAL1 | EVALUATION PLATFORM SOIC HI5860 |

| REC5-0505DRW/H2/A | CONV DC/DC 5W 4.5-9VIN +/-05VOUT |

| REC5-483.3DRW/H2/C | CONV DC/DC 5W 36-72VIN +/-3.3V |

| GCM22DCMH | CONN EDGECARD 44POS .156 WW |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7764EBZ | 制造商:Analog Devices 功能描述:EVAL BD FOR AD7764 - Bulk |

| EVAL-AD7764EDZ | 功能描述:BOARD EVAL AD7764 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7765EBZ | 制造商:Analog Devices 功能描述:EVAL BOARD 24BIT, 312KSPS, 109DB - Bulk |

| EVAL-AD7765EDZ | 功能描述:BOARD EVAL AD7765 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7766-1EDZ | 功能描述:BOARD EVAL AD7766-1 64KSPS 111DB RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

发布紧急采购,3分钟左右您将得到回复。