- 您现在的位置:买卖IC网 > PDF目录223858 > GMZAN3T (Electronic Theatre Controls, Inc.) XGA ALALOG INTERFACE LCD MONITOR CONTROLLER PDF资料下载

参数资料

| 型号: | GMZAN3T |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | XGA ALALOG INTERFACE LCD MONITOR CONTROLLER |

| 中文描述: | ALALOG的XGA液晶显示器接口控制器 |

| 文件页数: | 38/53页 |

| 文件大小: | 556K |

| 代理商: | GMZAN3T |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页

gmZAN3 Preliminary Data Sheet

C0523-DAT-01G

43

July 2003

Ge nes i s Microc hip Confid e n tia l

http:// w ww . g enesis-mic r ochip.com

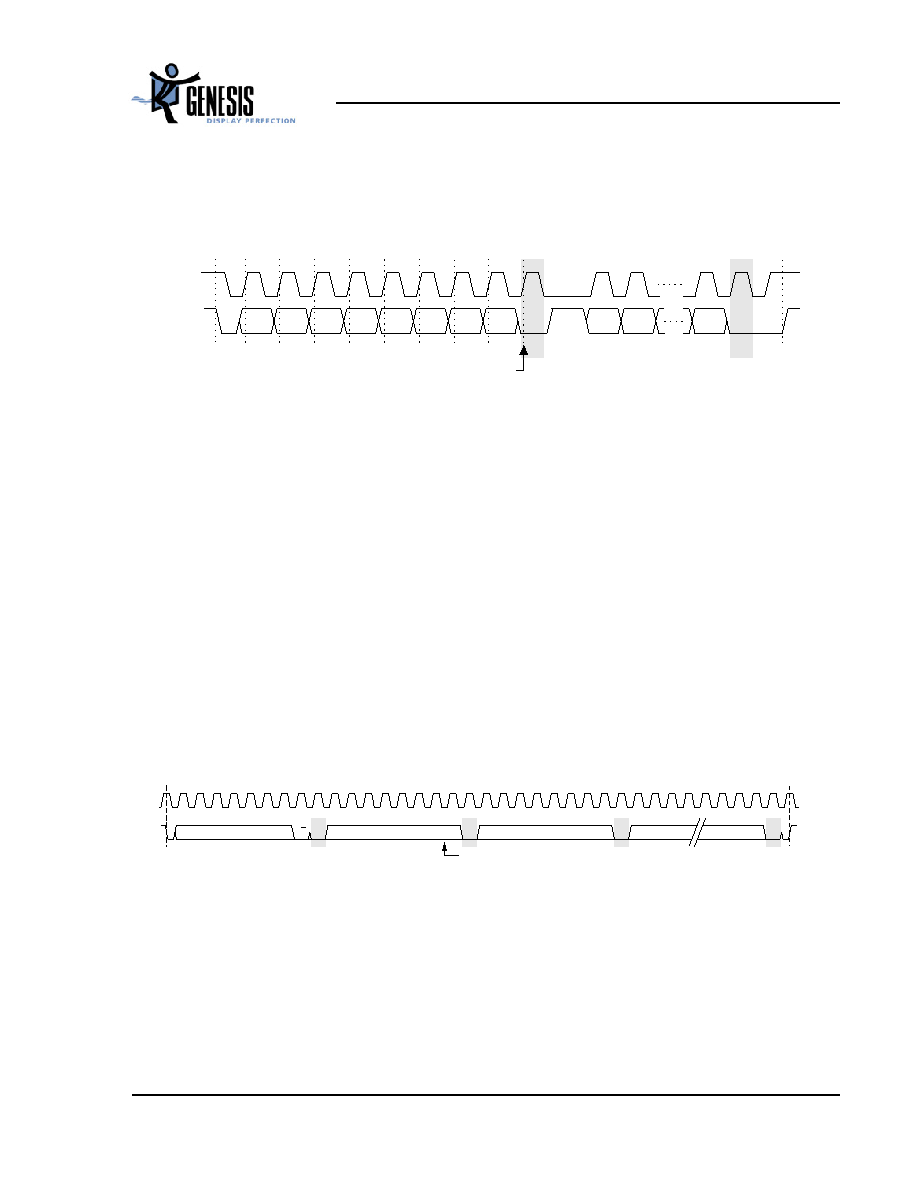

A 2-wire data transfer consists of a stream of serially transmitted bytes formatted as shown in the figure

below. A transfer is initiated (START) by a high-to-low transition on HFS while HCLK is held high. A

transfer is terminated by a STOP (a low-to-high transition on HFS while HCLK is held high) or by a

START (to begin another transfer). The HFS signal must be stable when HCLK is high, it may only

change when HCLK is low (to avoid being misinterpreted as START or STOP).

ADDRESS BYTE

HFS

123

789

HCLK

456

12

89

DATA BYTE

ACK

START

STOP

Receiver acknowledges by holding SDA low

R/W

A6

A1

A2

A3

A4

A5

A0

D6

D7

D0

Figure 26.

2-Wire Protocol Data Transfer

Each transaction on the HFS is in integer multiples of 8 bits (i.e. bytes). The number of bytes that can be

transmitted per transfer is unrestricted. Each byte is transmitted with the most significant bit (MSB) first.

After the eight data bits, the master releases the HFS line and the receiver asserts the HFS line low to

acknowledge receipt of the data. The master device generates the HCLK pulse during the acknowledge

cycle. The addressed receiver is obliged to acknowledge each byte that has been received.

The Write Address Increment and the Write Address No Increment operations allow one or multiple

registers to be programmed with only sending one start address. In Write Address Increment, the address

pointer is automatically incremented after each byte has been sent and written. The transmission data

stream for this mode is illustrated in Figure 27 below. The highlighted sections of the waveform represent

moments when the transmitting device must release the HFS line and wait for an acknowledgement from

the gmZAN3 (the slave receiver).

ACK

OPERATIONCODE

START

HFS

HCLK

STOP

DEVICEADDRESS

REGISTERADDRESS

DATA

R/W

ACK

12

34

5

6

789

12

34

5

6

789

12

3

4

5

6

789

1

2

9

A8

TwoMSBs of register address

A9

Figure 27.

2-Wire Write Operations (0x1x and 0x2x)

The Read Address Increment (0x90) and Read Address No Increment (0xA0) operations are illustrated in

Figure 28. The highlighted sections of the waveform represent moments when the transmitting device

must release the HFS line and waits for an acknowledgement from the master receiver.

Note that on the last byte read, no acknowledgement is issued to terminate the transfer.

相关PDF资料 |

PDF描述 |

|---|---|

| GMZJ12CT/R | 12.05 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| GMZJ12C | 12.05 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| GMZJ13B | 12.88 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| GMZJ13C | 13.33 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| GMZJ15AT/R | 13.79 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| GMZJ | 制造商:RECTRON 制造商全称:Rectron Semiconductor 功能描述:Micro MELF ZENER DIODE 2.5% 500mW |

| GMZJ10 | 制造商:RECTRON 制造商全称:Rectron Semiconductor 功能描述:Micro MELF ZENER DIODE 2.5% 500mW |

| GMZJ10A _R1 _10001 | 制造商:PanJit Touch Screens 功能描述: |

| GMZJ10A_ R2 _10001 | 制造商:PanJit Touch Screens 功能描述: |

| GMZJ10B _R1 _10001 | 制造商:PanJit Touch Screens 功能描述: |

发布紧急采购,3分钟左右您将得到回复。