参数资料

| 型号: | HW-SPAR3-SK-UNI-G |

| 厂商: | Xilinx Inc |

| 文件页数: | 24/64页 |

| 文件大小: | 0K |

| 描述: | KIT STARTER SPARTAN-3 |

| 产品变化通告: | Adapter Replacement 23/May/2008 Development Systems Discontinuation 22/Jun/2009 |

| 标准包装: | 1 |

| 系列: | Spartan-3 |

| 类型: | FPGA 配置 |

| 适用于相关产品: | Spartan-3 |

| 所含物品: | 面板、缆线、软件、数据表和用户手册 |

| 其它名称: | 122-1521 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

�� �

�

�

�R�

�Chapter� 5:� VGA� Port�

�Modern� VGA� displays� support� multiple� display� resolutions,� and� the� VGA� controller�

�dictates� the� resolution� by� producing� timing� signals� to� control� the� raster� patterns.� The�

�controller� produces� TTL-level� synchronizing� pulses� that� set� the� frequency� at� which� current�

�flows� through� the� deflection� coils,� and� it� ensures� that� pixel� or� video� data� is� applied� to� the�

�electron� guns� at� the� correct� time.�

�Video� data� typically� comes� from� a� video� refresh� memory� with� one� or� more� bytes� assigned�

�to� each� pixel� location.� The� Spartan-3� Starter� Kit� board� uses� three� bits� per� pixel,� producing�

�one� of� the� eight� possible� colors� shown� in� Table� 5-2� .� The� controller� indexes� into� the� video�

�data� buffer� as� the� beams� move� across� the� display.� The� controller� then� retrieves� and� applies�

�video� data� to� the� display� at� precisely� the� time� the� electron� beam� is� moving� across� a� given�

�pixel.�

�As� shown� in� Figure� 5-2� ,� the� VGA� controller� generates� the� HS� (horizontal� sync)� and� VS�

�(vertical� sync)� timings� signals� and� coordinates� the� delivery� of� video� data� on� each� pixel�

�clock.� The� pixel� clock� defines� the� time� available� to� display� one� pixel� of� information.� The� VS�

�signal� defines� the� “refresh”� frequency� of� the� display,� or� the� frequency� at� which� all�

�information� on� the� display� is� redrawn.� The� minimum� refresh� frequency� is� a� function� of� the�

�display’s� phosphor� and� electron� beam� intensity,� with� practical� refresh� frequencies� in� the�

�60� Hz� to� 120� Hz� range.� The� number� of� horizontal� lines� displayed� at� a� given� refresh�

�frequency� defines� the� horizontal� “retrace”� frequency.�

�VGA� Signal� Timing�

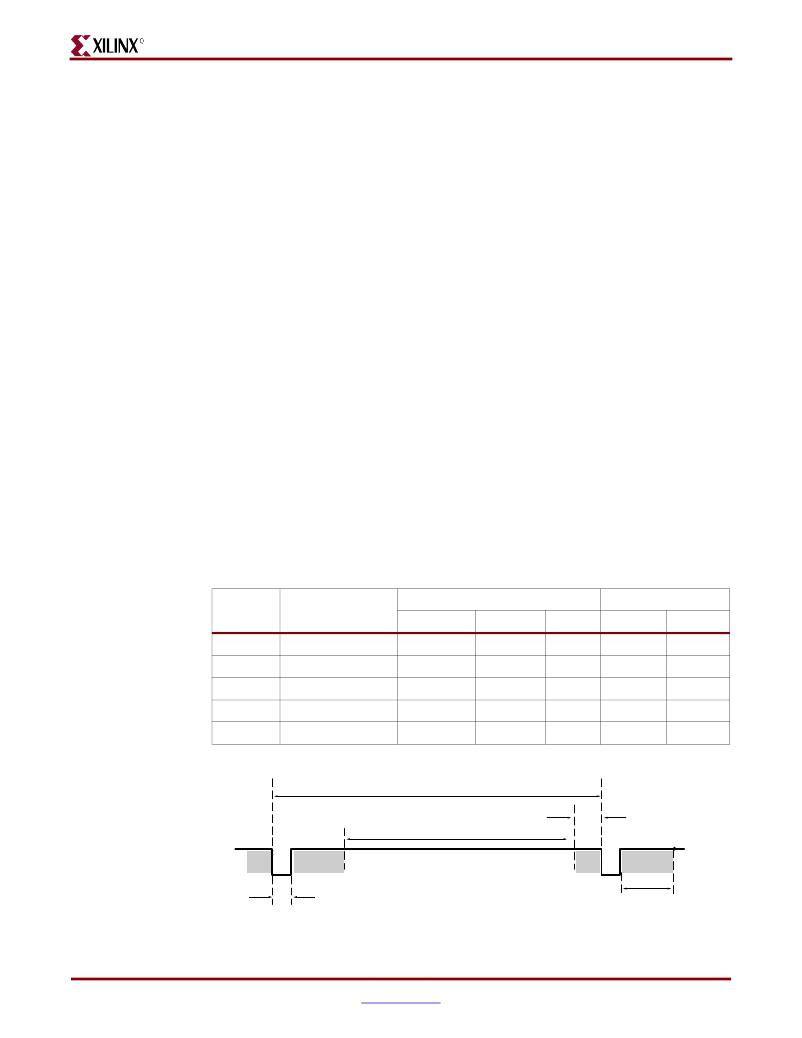

�The� signal� timings� in� Table� 5-3� are� derived� for� a� 640-pixel� by� 480-row� display� using� a�

�25� MHz� pixel� clock� and� 60� Hz� ±1� refresh.� Figure� 5-3� shows� the� relation� between� each� of� the�

�timing� symbols.� The� timing� for� the� sync� pulse� width� (T� PW� )� and� front� and� back� porch�

�intervals� (T� FP� and� T� BP� )� are� based� on� observations� from� various� VGA� displays.� The� front�

�and� back� porch� intervals� are� the� pre-� and� post-sync� pulse� times.� Information� cannot� be�

�displayed� during� these� times.�

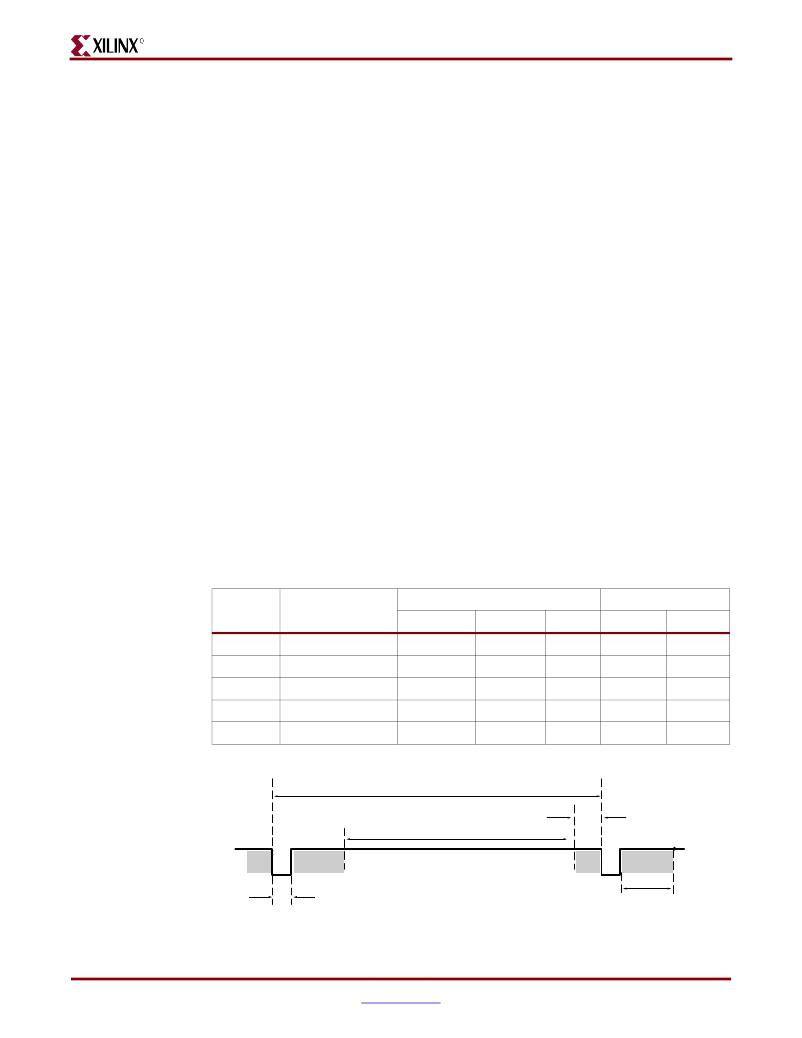

�Table� 5-3:�

�640x480� Mode� VGA� Timing�

�Symbol�

�Parameter�

�Time�

�Vertical� Sync�

�Clocks�

�Lines�

�Horizontal� Sync�

�Time� Clocks�

�T� S�

�T� DISP�

�T� PW�

�T� FP�

�T� BP�

�Sync� pulse� time�

�Display� time�

�Pulse� width�

�Front� porch�

�Back� porch�

�16.7� ms�

�15.36� ms�

�64� μ� s�

�320� μ� s�

�928� μ� s�

�416,800�

�384,000�

�1,600�

�8,000�

�23,200�

�521�

�480�

�2�

�10�

�29�

�32� μ� s�

�25.6� μ� s�

�3.84� μ� s�

�640� ns�

�1.92� μ� s�

�800�

�640�

�96�

�16�

�48�

�T� S�

�T� PW�

�T� DISP�

�T� FP�

�T� BP�

�UG130_c5_03_051305�

�Figure� 5-3:�

�VGA� Control� Timing�

�24�

��Spartan-3� FPGA� Starter� Kit� Board� User� Guide�

�UG130� (v1.2)� June� 20,� 2008�

�相关PDF资料 |

PDF描述 |

|---|---|

| HW-SPAR3E-DISP-DK-UNI-G | KIT DEV SPARTAN3E DISPLAY |

| HW-SPAR3E-SK-UK-G | KIT STARTER SPARTAN-3E |

| HW-USB-II-G | PLATFORM CABLE USB II |

| HW-USBN-2A | ACCY USB DOWNLOAD CABLE STD SPD |

| HW-V4-ML401-USA | EVALUATION PLATFORM VIRTEX-4 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HW-T126 | 制造商:IDEC Corporation 功能描述:120V/6V Xfrmr w/G Trmnls |

| HW-T246 | 制造商:IDEC CORPORATION 功能描述:240V/6V Xfrmr w/G Trmnls |

| HWT9/17 | 制造商:Talco Tool Storage 功能描述:9 TRAY CANTILEVER TOOLBOX |

| HW-USB-1A | 功能描述:程序设计器配件 ispDOWNLOAD Cable - USB CONNECTION RoHS:否 制造商:Lattice 产品:ispDOWNLOAD Cables 用于:In-system Programming |

| HW-USB-2A | 功能描述:程序设计器配件 ispDOWNLOAD Cable USB Connection RoHS:否 制造商:Lattice 产品:ispDOWNLOAD Cables 用于:In-system Programming |

发布紧急采购,3分钟左右您将得到回复。