参数资料

| 型号: | HW-SPAR3-SK-UNI-G |

| 厂商: | Xilinx Inc |

| 文件页数: | 29/64页 |

| 文件大小: | 0K |

| 描述: | KIT STARTER SPARTAN-3 |

| 产品变化通告: | Adapter Replacement 23/May/2008 Development Systems Discontinuation 22/Jun/2009 |

| 标准包装: | 1 |

| 系列: | Spartan-3 |

| 类型: | FPGA 配置 |

| 适用于相关产品: | Spartan-3 |

| 所含物品: | 面板、缆线、软件、数据表和用户手册 |

| 其它名称: | 122-1521 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

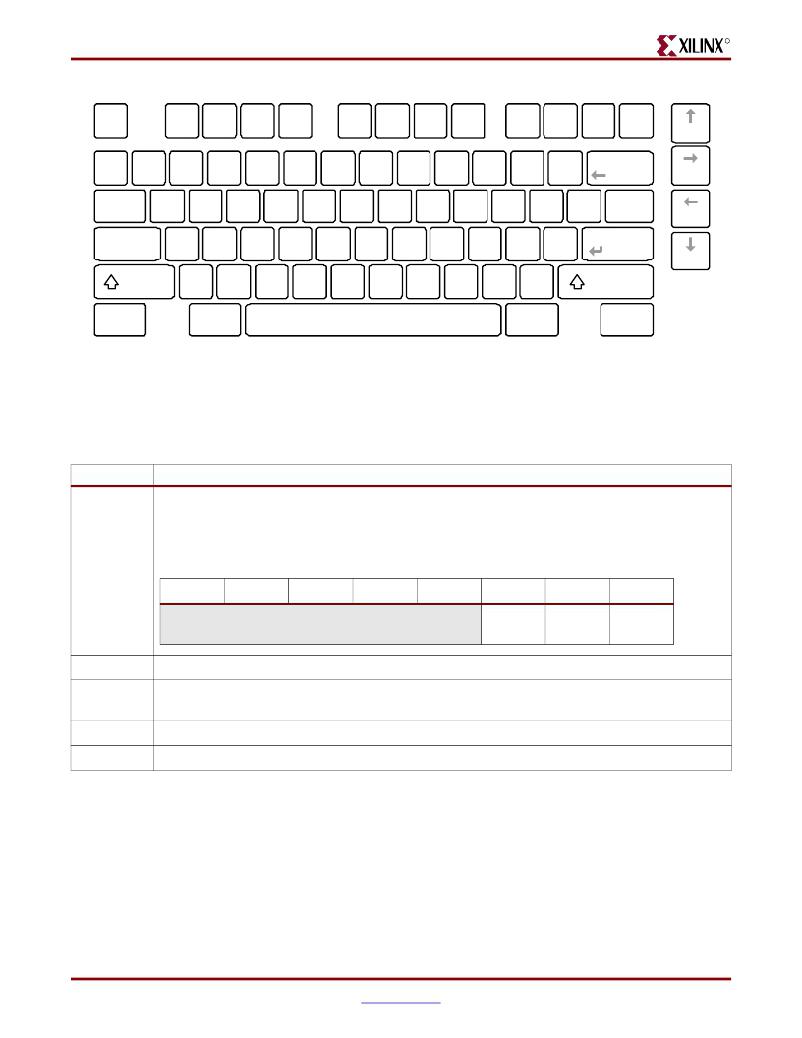

�� �

�

�

�Keyboard�

�R�

�ESC�

�F1�

�F2�

�F3�

�F4�

�F5�

�F6�

�F7�

�F8�

�F9�

�F10�

�F11�

�F12�

�76�

�05�

�06�

�04�

�0C�

�03�

�0B�

�83�

�0A�

�01�

�09�

�78�

�07�

�E0� 75�

�`~�

�1!�

�2@�

�3#�

�4$�

�5%�

�6^�

�7&�

�8*�

�9(�

�0)�

�-_�

�=+�

�Back� Space�

�0E�

�TAB�

�16�

�Q�

�1E�

�W�

�26�

�E�

�25�

�R�

�2E�

�T�

�36�

�Y�

�3D�

�U�

�3E�

�I�

�46�

�O�

�45�

�P�

�4E�

�[{�

�55�

�]}�

�66�

�\|�

�E0� 74�

�0D�

�Caps� Lock�

�15�

�A�

�1D�

�S�

�24�

�D�

�2D�

�F�

�2C�

�G�

�35�

�H�

�3C�

�J�

�43�

�K�

�44�

�L�

�4D�

�;:�

�54�

�'"�

�5B�

�5D�

�Enter�

�E0� 6B�

�58�

�Shift�

�12�

�1C�

�Z�

�1Z�

�1B�

�X�

�22�

�23�

�C�

�21�

�2B�

�V�

�2A�

�34�

�B�

�32�

�33�

�N�

�31�

�3B�

�M�

�3A�

�42�

�,<�

�41�

�4B�

�>.�

�49�

�4C�

�/?�

�4A�

�52�

�5A�

�Shift�

�59�

�E0� 72�

�Ctrl�

�14�

�Alt�

�11�

�Space�

�29�

�Alt�

�E0� 11�

�Ctrl�

�E0� 14�

�UG130_c6_03_042404�

�Figure� 6-3:�

�PS/2� Keyboard� Scan� Codes�

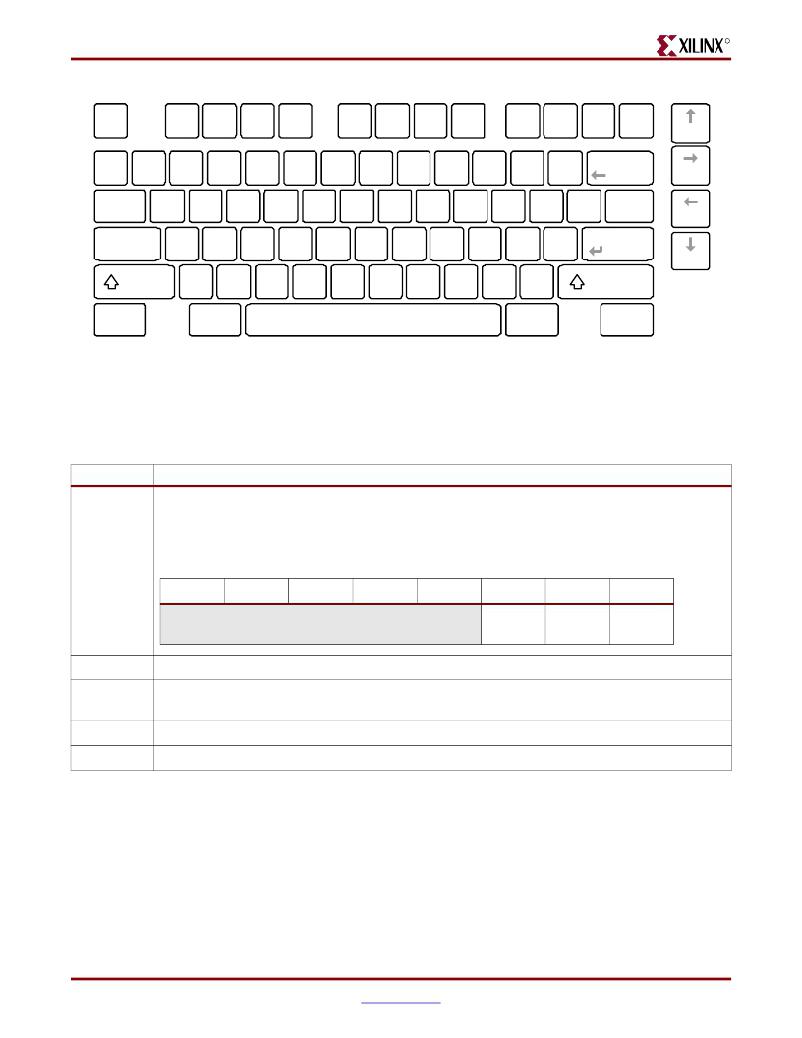

�The� host� can� also� send� data� to� the� keyboard.� Table� 6-3� provides� a� short� list� of� some� often-�

�used� commands.�

�Table� 6-3:�

�Common� PS/2� Keyboard� Commands�

�Command�

�ED�

�Description�

�Turn� on/off� Num� Lock,� Caps� Lock,� and� Scroll� Lock� LEDs.� The� keyboard� acknowledges� receipt� of�

�an� “ED”� command� by� replying� with� an� “FA”,� after� which� the� host� sends� another� byte� to� set� LED�

�status.� The� bit� positions� for� the� keyboard� LEDs� appear� in� Table� 6-4� .� Write� a� ‘1’� to� the� specific� bit� to�

�illuminate� the� associated� keyboard� LED.�

�Table� 6-4:� Keyboard� LED� Control�

�7�

�6�

�5�

�4�

�3�

�2�

�1�

�0�

�Ignored�

�Caps�

�Lock�

�Num�

�Lock�

�Scroll�

�Lock�

�EE�

�F3�

�FE�

�FF�

�Echo.� Upon� receiving� an� echo� command,� the� keyboard� replies� with� the� same� scan� code� “EE”.�

�Set� scan� code� repeat� rate.� The� keyboard� acknowledges� receipt� of� an� “F3”� by� returning� an� “FA”,�

�after� which� the� host� sends� a� second� byte� to� set� the� repeat� rate.�

�Resend.� Upon� receiving� a� resend� command,� the� keyboard� resends� the� last� scan� code� sent.�

�Reset.� Resets� the� keyboard.�

�The� keyboard� sends� data� to� the� host� only� when� both� the� data� and� clock� lines� are� High,� the�

�Idle� state.�

�Because� the� host� is� the� “bus� master”,� the� keyboard� checks� whether� the� host� is� sending� data�

�before� driving� the� bus.� The� clock� line� can� be� used� as� a� “clear� to� send”� signal.� If� the� host�

�pulls� the� clock� line� Low,� the� keyboard� must� not� send� any� data� until� the� clock� is� released.�

�The� keyboard� sends� data� to� the� host� in� 11-bit� words� that� contain� a� ‘0’� start� bit,� followed� by�

�eight� bits� of� scan� code� (LSB� first),� followed� by� an� odd� parity� bit� and� terminated� with� a� ‘1’�

�stop� bit.� When� the� keyboard� sends� data,� it� generates� 11� clock� transitions� at� around� 20� to�

�30� kHz,� and� data� is� valid� on� the� falling� edge� of� the� clock� as� shown� in� Figure� 6-2� .�

�Spartan-3� FPGA� Starter� Kit� Board� User� Guide�

�UG130� (v1.2)� June� 20,� 2008�

��29�

�相关PDF资料 |

PDF描述 |

|---|---|

| HW-SPAR3E-DISP-DK-UNI-G | KIT DEV SPARTAN3E DISPLAY |

| HW-SPAR3E-SK-UK-G | KIT STARTER SPARTAN-3E |

| HW-USB-II-G | PLATFORM CABLE USB II |

| HW-USBN-2A | ACCY USB DOWNLOAD CABLE STD SPD |

| HW-V4-ML401-USA | EVALUATION PLATFORM VIRTEX-4 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HW-T126 | 制造商:IDEC Corporation 功能描述:120V/6V Xfrmr w/G Trmnls |

| HW-T246 | 制造商:IDEC CORPORATION 功能描述:240V/6V Xfrmr w/G Trmnls |

| HWT9/17 | 制造商:Talco Tool Storage 功能描述:9 TRAY CANTILEVER TOOLBOX |

| HW-USB-1A | 功能描述:程序设计器配件 ispDOWNLOAD Cable - USB CONNECTION RoHS:否 制造商:Lattice 产品:ispDOWNLOAD Cables 用于:In-system Programming |

| HW-USB-2A | 功能描述:程序设计器配件 ispDOWNLOAD Cable USB Connection RoHS:否 制造商:Lattice 产品:ispDOWNLOAD Cables 用于:In-system Programming |

发布紧急采购,3分钟左右您将得到回复。