- 您现在的位置:买卖IC网 > PDF目录224000 > HYS72T64000EP-3.7-B2 (QIMONDA AG) 64M X 72 DDR DRAM MODULE, DMA240 PDF资料下载

参数资料

| 型号: | HYS72T64000EP-3.7-B2 |

| 厂商: | QIMONDA AG |

| 元件分类: | DRAM |

| 英文描述: | 64M X 72 DDR DRAM MODULE, DMA240 |

| 封装: | GREEN, RDIMM-240 |

| 文件页数: | 16/64页 |

| 文件大小: | 3411K |

| 代理商: | HYS72T64000EP-3.7-B2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

HYS72T[64/128/256]xx0EP–[2.5/25F/3/3S/3.7]–B2

Registered DDR2 SDRAM Modules

Internet Data Sheet

Rev. 1.02, 2008-06

23

07312007-HYD2-P177

1)

V

DDQ = 1.8 V ± 0.1V; VDD = 1.8 V ± 0.1 V.

2) Timing that is not specified is illegal and after such an event, in order to guarantee proper operation, the DRAM must be powered down

and then restarted through the specified initialization sequence before normal operation can continue.

3) Timings are guaranteed with CK/CK differential Slew Rate of 2.0 V/ns. For DQS signals timings are guaranteed with a differential Slew

Rate of 2.0 V/ns in differential strobe mode and a Slew Rate of 1 V/ns in single ended mode.

4) The CK / CK input reference level (for timing reference to CK / CK) is the point at which CK and CK cross. The DQS / DQS, RDQS / RDQS,

input reference level is the crosspoint when in differential strobe mode.

5) Inputs are not recognized as valid until

V

REF stabilizes. During the period before VREF stabilizes, CKE = 0.2 x VDDQ is recognized as low.

6) The output timing reference voltage level is

V

TT.

7) For each of the terms, if not already an integer, round to the next highest integer.

t

CK refers to the application clock period. WR refers to

the WR parameter stored in the MR.

8) The clock frequency is allowed to change during self-refresh mode or precharge power-down mode.

9) For timing definition, refer to the Component data sheet.

10) Consists of data pin skew and output pattern effects, and p-channel to n-channel variation of the output drivers as well as output Slew Rate

mis-match between DQS / DQS and associated DQ in any given cycle.

11) MIN (

t

CL, tCH) refers to the smaller of the actual clock low time and the actual clock high time as provided to the device (i.e. this value can

be greater than the minimum specification limits for

t

CL and tCH).

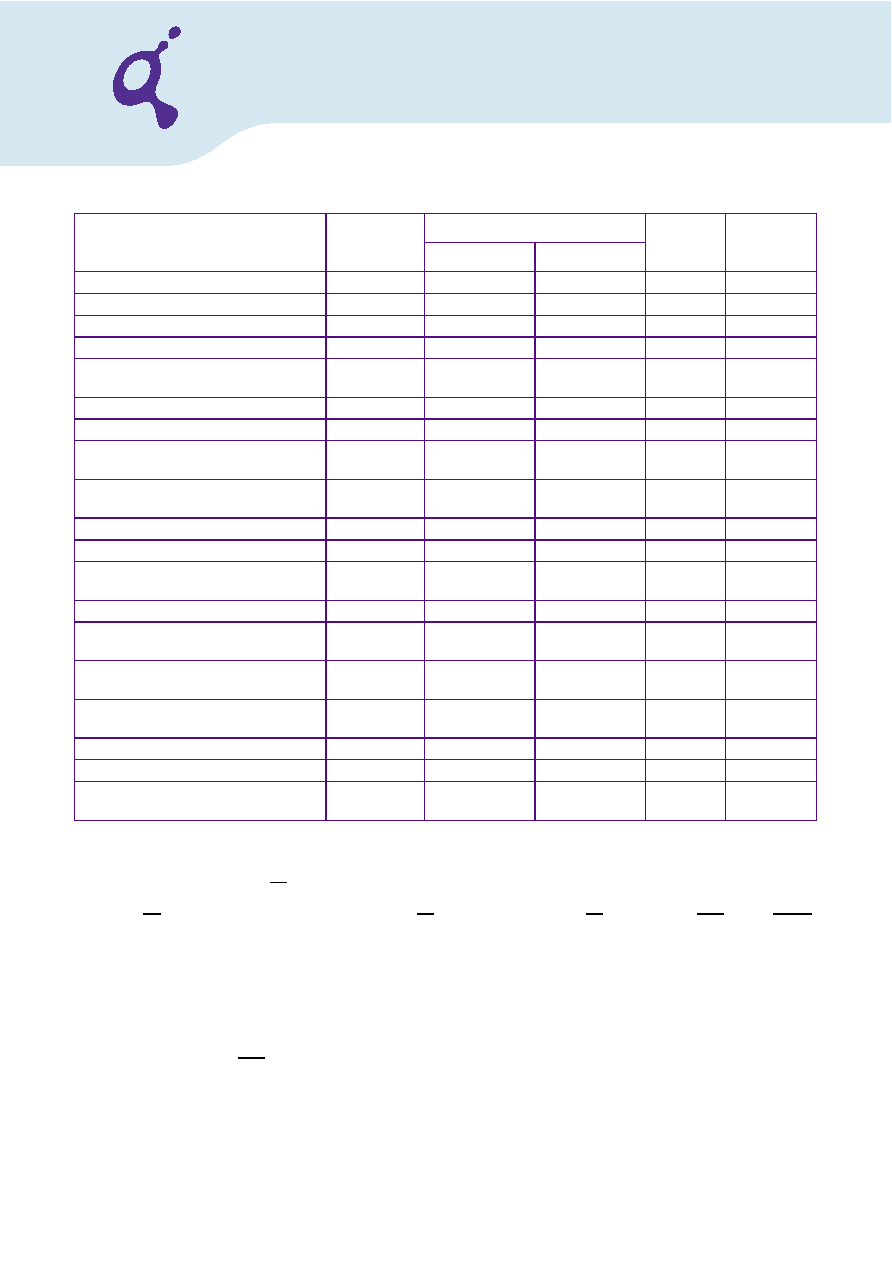

Data output hold time from DQS

t

QH

t

HP –tQHS

—

Data hold skew factor

t

QHS

—

400

ps

Average periodic refresh Interval

t

REFI

—7.8

μs

Average periodic refresh Interval

t

REFI

—3.9

μs

Auto-Refresh to Active/Auto-Refresh

command period

t

RFC

105

—

ns

Read preamble

t

RPRE

0.9

1.1

t

CK

Read postamble

t

RPST

0.40

0.60

t

CK

Active bank A to Active bank B command

period for 1 KB page size

t

RRD

7.5

—

ns

Internal Read to Precharge command

delay

t

RTP

7.5

—

ns

Write preamble

t

WPRE

0.25

—

t

CK

Write postamble

t

WPST

0.40

0.60

t

CK

Write recovery time for write without

Auto-Precharge

t

WR

15

—

ns

Internal Write to Read command delay

t

WTR

7.5

—

ns

Exit power down to any valid command

(other than NOP or Deselect)

t

XARD

2—

t

CK

Exit active power-down mode to Read

command (slow exit, lower power)

t

XARDS

6 – AL

—

t

CK

Exit precharge power-down to any valid

command (other than NOP or Deselect)

t

XP

2—

t

CK

Exit Self-Refresh to non-Read command

t

XSNR

t

RFC +10

—

ns

Exit Self-Refresh to Read command

t

XSRD

200

—

t

CK

Write recovery time for write with Auto-

Precharge

WR

t

WR/tCK

t

CK

Parameter

Symbol

DDR2–533

Unit

Notes

1)2)3)4)5)

6)

Min.

Max.

相关PDF资料 |

PDF描述 |

|---|---|

| HZ20-1 | 19.25 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-35 |

| HZ6B1L | 5.65 V, 0.4 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-35 |

| HZ9.1CP | 9.65 V, 1 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-41 |

| HZB6.8MWA | 6.8 V, 0.2 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| HZF24BPTR | 0.9 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HYS72T64000EU-2.5-B2 | 制造商:QIMONDA 制造商全称:QIMONDA 功能描述:240-Pin unbuffered DDR2 SDRAM Modules |

| HYS72T64000EU-25F-B2 | 制造商:QIMONDA 制造商全称:QIMONDA 功能描述:240-Pin unbuffered DDR2 SDRAM Modules |

| HYS72T64000EU-3.7-B2 | 制造商:QIMONDA 制造商全称:QIMONDA 功能描述:240-Pin unbuffered DDR2 SDRAM Modules |

| HYS72T64000EU-3-B2 | 制造商:QIMONDA 制造商全称:QIMONDA 功能描述:240-Pin unbuffered DDR2 SDRAM Modules |

| HYS72T64000EU-3S-B2 | 制造商:QIMONDA 制造商全称:QIMONDA 功能描述:240-Pin unbuffered DDR2 SDRAM Modules |

发布紧急采购,3分钟左右您将得到回复。