- 您现在的位置:买卖IC网 > PDF目录10729 > ICS1893BKILF (IDT, Integrated Device Technology Inc)PHYCEIVER LOW PWR 3.3V 56-VQFN PDF资料下载

参数资料

| 型号: | ICS1893BKILF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 76/133页 |

| 文件大小: | 0K |

| 描述: | PHYCEIVER LOW PWR 3.3V 56-VQFN |

| 标准包装: | 260 |

| 系列: | PHYceiver™ |

| 类型: | PHY 收发器 |

| 规程: | MII |

| 电源电压: | 3.14 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 56-VFQFN 裸露焊盘 |

| 供应商设备封装: | 56-VFQFP-EP(8x8) |

| 包装: | 管件 |

| 其它名称: | 1893BKILF 800-2354-5 ICS1893BKILF-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页当前第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页

Chapter 6 Functional Blocks

ICS1893BF, Rev. F, 5/13/10

May, 2010

47

ICS1893BF Data Sheet Rev. F - Release

Copyright 2009, IDT, Inc.

All rights reserved.

Note: The Management Frame Structure starts from and returns to an IDLE condition. However, the IDLE

periods are not part of the Management Frame Structure.

6.6.2.1 Management Frame Preamble

The ICS1893BF continually monitors its serial management interface for either valid data or a Management

Frame (MF) Preamble, based upon the setting of the MF Preamble Suppression bit, 1.6. When the MF

Preamble Suppression is disabled, an ICS1893BF waits for a MF Preamble which indicates the start of an

STA transaction. A Management Frame Preamble is a pattern of 32 contiguous logic one bits on the MDIO

pin, along with 32 corresponding clock cycles on the MDC pin.

The ICS1893BF supports the Management Frame (MF) Preamble Suppression capability on its

Management Interface, thereby providing a method to shorten the Management Frame and provide an STA

with faster access to the Management Registers.

The ability to process Management Frames that do not have a preamble is provided by the Management

Frame Preamble Suppression bit, (bit 1.6 in the ICS1893BF’s Status Register). This is an ISO/IEC defined

status bit that is intended to provide an indication of whether or not a PHY supports the MF Preamble

Suppression feature. In order to maintain backward compatibility with the ICS1890, which did not support

MF Preamble Suppression, the ICS1893BF MF Preamble Suppression bit is a Command Override Write

bit which defaults to a logic zero. An STA can enable MF Preamble Suppression by writing a logic one to bit

1.6 subsequent to a write of logic one to the Command Override bit, 16.15. For an explanation of the

Command Override Write bits, see Section 7.1.2, “Management Register Bit Access”.

6.6.2.2 Management Frame Start

A valid Management Frame includes a start-of-frame delimiter, SFD, immediately following the preamble.

The SFD bit pattern is 01b and is synchronous with two clock cycles on the MDC pin.

6.6.2.3 Management Frame Operation Code

A valid Management Frame includes an operation code (OP) immediately following the start-of-frame

delimiter. There are two valid operation codes: one for reading from a management register, 10b, and one

for writing to a management register, 01b. The ICS1893BF does not respond to the codes 00b and 11b,

which the ISO/IEC specification defines as invalid.

6.6.2.4 Management Frame PHY Address

The two-wire, Serial Management Interface is specified to allow busing (that is, the sharing of the two wires

among multiple PHYs). The Management Frame includes a 5-bit PHY Address field, PHYAD, allowing for

32 unique addresses. An STA uniquely identifies each of the PHYs that share a single serial management

interface by using this 5-bit PHY Address field, PHYAD.

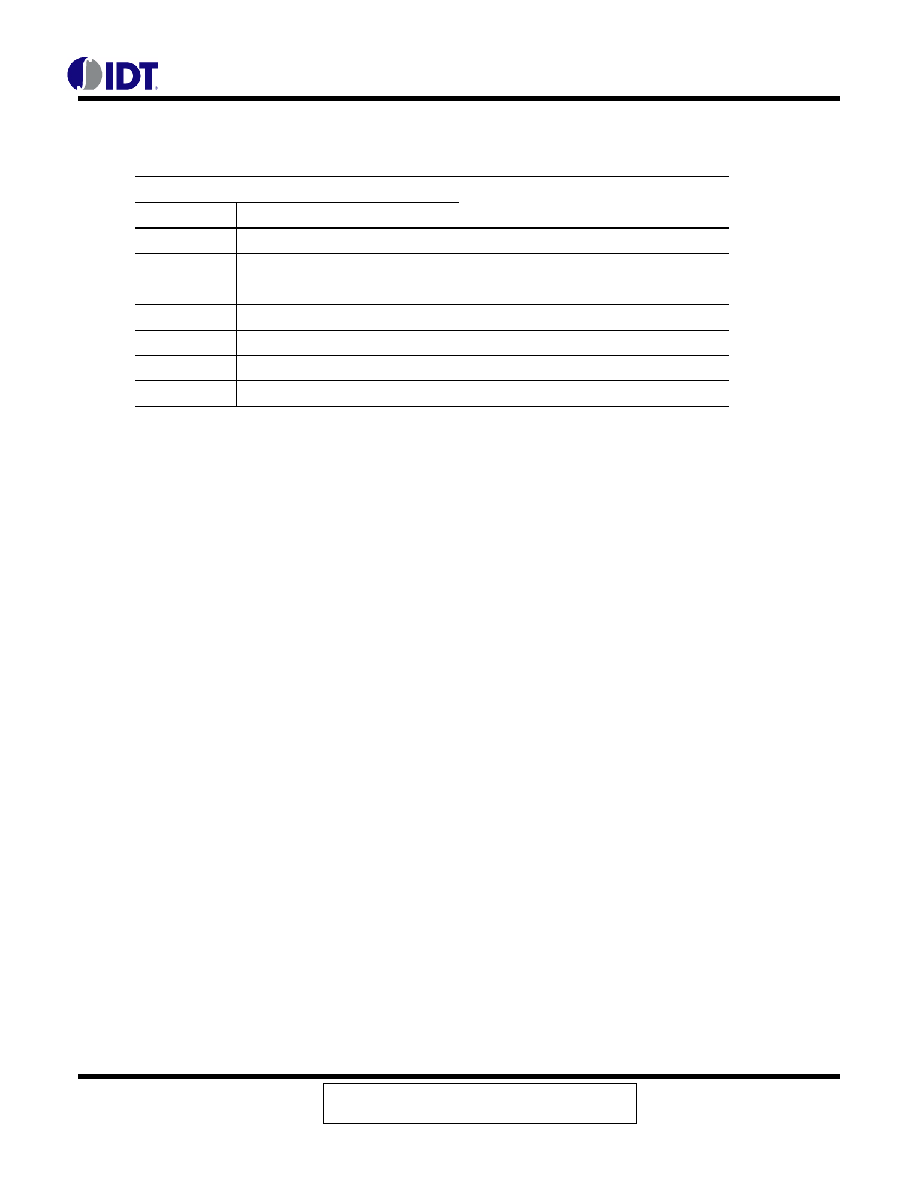

Table 6-1. Management Frame Structure Summary

Frame Field

Data

Comment

Acronym

Frame Function

PRE

Preamble (Bit 1.6)

11..11

32 ones

SFD

Start of Frame

01

2 bits

OP

Operation Code

10/01 (read/write)

2 bits

PHYAD

PHY Address (Bits 16.10:6)

AAAAA

5 bits

REGAD

Register Address

RRRRR

5 bits

TA

Turnaround

Z0/10 (read/write)

2 bits

DATA

Data

DDD..DD

16 bits

相关PDF资料 |

PDF描述 |

|---|---|

| VE-25K-MY-B1 | CONVERTER MOD DC/DC 40V 50W |

| MAX912CPE+ | IC COMPARATOR LP 16-DIP |

| VE-2NF-IW | CONVERTER MOD DC/DC 72V 100W |

| VE-JND-MY-F4 | CONVERTER MOD DC/DC 85V 50W |

| VE-25J-MY-B1 | CONVERTER MOD DC/DC 36V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1893BKILFT | 功能描述:PHYCEIVER LOW PWR 3.3V 56-VQFN RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:PHYceiver™ 标准包装:1 系列:- 类型:线路收发器 驱动器/接收器数:5/3 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:Digi-Reel® 产品目录页面:918 (CN2011-ZH PDF) 其它名称:296-25096-6 |

| ICS1893BKIT | 功能描述:PHYCEIVER LOW PWR 3.3V 56-VQFN RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:PHYceiver™ 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| ICS1893BKLF | 功能描述:PHYCEIVER LOW PWR 3.3V 56-VQFN RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:PHYceiver™ 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| ICS1893BKLFT | 功能描述:PHYCEIVER LOW PWR 3.3V 56-VQFN RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:PHYceiver™ 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| ICS1893BKT | 功能描述:PHYCEIVER LOW PWR 3.3V 56-VQFN RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:PHYceiver™ 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。