- 您现在的位置:买卖IC网 > PDF目录261237 > ICS527R-01T 527 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 PDF资料下载

参数资料

| 型号: | ICS527R-01T |

| 元件分类: | 时钟及定时 |

| 英文描述: | 527 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 封装: | 0.150 INCH, 0.025 INCH PITCH, MO-153, SSOP-28 |

| 文件页数: | 2/9页 |

| 文件大小: | 176K |

| 代理商: | ICS527R-01T |

Clock Slicer User Configurable Zero Delay Buffer

MDS 527-01 E

2

Revision 032405

Integrated Circuit Systems, Inc.

● 525 Race Street, San Jose, CA 95126 ● tel (408) 297-1201 ● www.icst.com

ICS527-01

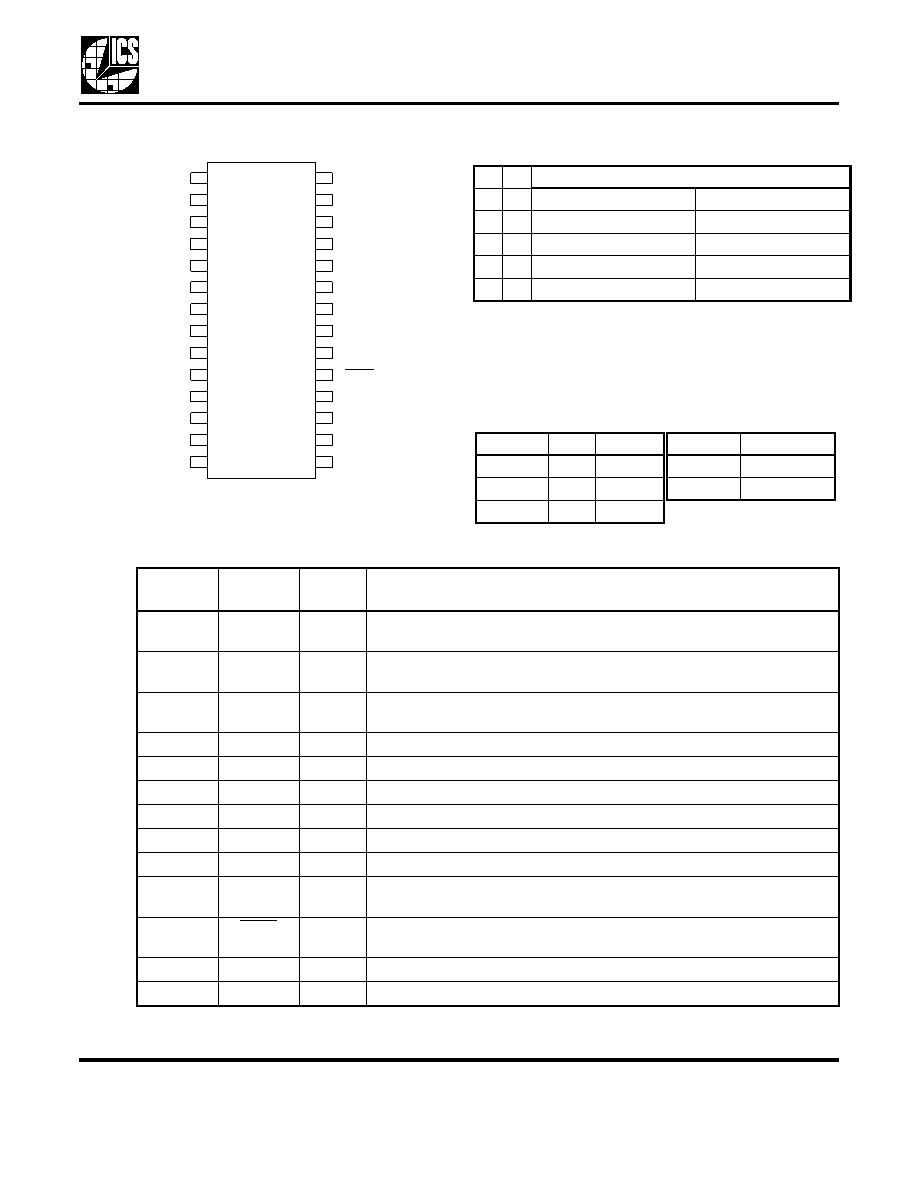

Pin Assignment

28 pin 150 mil body SSOP

Frequency Range Table

To cover the range from 10 to 18 MHz (0 to 70°C) and 8

to 16 MHz (-40 to 85°C), select address 01 to generate

2x your desired output frequency, then configure CLK2

to generate CLK1/2.

Pin Descriptions

18

7

17

8

16

9

15

ICLK

10

FBIN

11

GND

12

CLK2

13

OECLK2

14

2XDRIVE

GND

PDTS

F6

F0

F5

F3

F1

F4

22

21

20

19

F2

CLK1

5

6

S1

VDD

24

23

R0

3

4

DIV2

S0

R1

26

25

R2

1

2

R5

R6

R3

28

27

R4

S1 S0

CLK1 Output Frequency (MHz)

Commercial (0 to 70°C)

Industrial (-40 to 85°C)

0

37 - 75

35 - 70

0

1

18 - 37

16 - 35

1

0

4 - 10

4 - 8

1

75 -160

70 - 140

CLK2 Operation Table

OECLK2

DIV2

CLK2

0X

Z

1

0

SYNC

11

CLK1/2

CLK Drive Select Table

2XDRIVE

Output Drive

0

12 mA

1

25 mA

Pin

Number

Pin

Name

Pin

Type

Pin Description

1,2, 24-28

R5, R6,

R0-R4

Input

Reference divider word input pins determined by user. Forms a binary number

from 0 to 127. Internal pull-up resistor.

3

DIV2

Input

Selects CLK2 function to output a SYNC signal or a divide by 2 of CLK1 based

on the table above. Internal pull-up resistor.

4, 5

S0, S1

Input

Select pins for output divider determined by user. See table above. Internal

pull-up resistor.

6, 23

VDD

Power

Connect to VDD.

7

ICLK

Input

Reference clock input.

8

FBIN

Input

Feedback clock input.

9, 20

GND

Power

Connect to ground.

10

OECLK2

Input

CLK2 Output Enable. CLK2 tri-stated when low. Internal pull-up resistor.

11

2XDRIVE

Input

Clock output drive strength doubled when high. Internal pull-up resistor.

12-18

F0-F6

Input

Feedback divider word input pins determined by user. Forms a binary number

from 0 to 127. Internal pull-up resistor.

19

PDTS

Input

Power Down. Active low. Turns off entire chip when low, both clock outputs are

tri-stated. Internal pull-up resistor.

21

CLK2

Output

Output clock 2. Can be SYNC output or a low skew divide by 2 of CLK1.

22

CLK1

Output

Output clock 1.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT74FCT2541CTD | FCT SERIES, 8-BIT DRIVER, TRUE OUTPUT, CDIP20 |

| IDTQS3LR384SO8 | DUAL 5-BIT DRIVER, TRUE OUTPUT, PDSO24 |

| IDT74LVCH646APG | LVC/LCX/Z SERIES, 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO24 |

| IDT74LVCH646ASO | LVC/LCX/Z SERIES, 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO24 |

| IDT74FCT540ATPY | FCT SERIES, 8-BIT DRIVER, INVERTED OUTPUT, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS527R-02 | 功能描述:IC CLOCK SLICER ZD BUFFER 28SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS527R-02I | 功能描述:IC CLOCK SLICER ZD BUFFER 28SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS527R-02ILF | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK SLICER ZD BUFFER 28SSOP |

| ICS527R-02ILFT | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK SLICER ZD BUFFER 28SSOP |

| ICS527R-02IT | 功能描述:IC CLOCK SLICER ZD BUFFER 28SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。