- 您现在的位置:买卖IC网 > PDF目录9149 > IDT5V49EE702NDGI (IDT, Integrated Device Technology Inc)IC PLL CLK GEN 200MHZ 28VQFN PDF资料下载

参数资料

| 型号: | IDT5V49EE702NDGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 34/34页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLK GEN 200MHZ 28VQFN |

| 产品培训模块: | VersaClock™ III Programmable Clocks |

| 特色产品: | VersaClock III Timing Devices |

| 标准包装: | 75 |

| 系列: | VersaClock™ III |

| 类型: | 时钟发生器,多路复用器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVTTL,晶体 |

| 输出: | HCSL,LVCMOS,LVDS,LVPECL,LVTTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:7 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 500MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-VFQFN 裸露焊盘 |

| 供应商设备封装: | 28-VFQFPN(4x4) |

| 包装: | 管件 |

| 其它名称: | 800-1918 IDT5V49EE702DLGI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页当前第34页

IDT5V49EE702

EEPROM PROGRAMMABLE CLOCK GENERATOR

CLOCK SYNTHESIZER

IDT EEPROM PROGRAMMABLE CLOCK GENERATOR

9

IDT5V49EE702

REV M 092412

Profile:

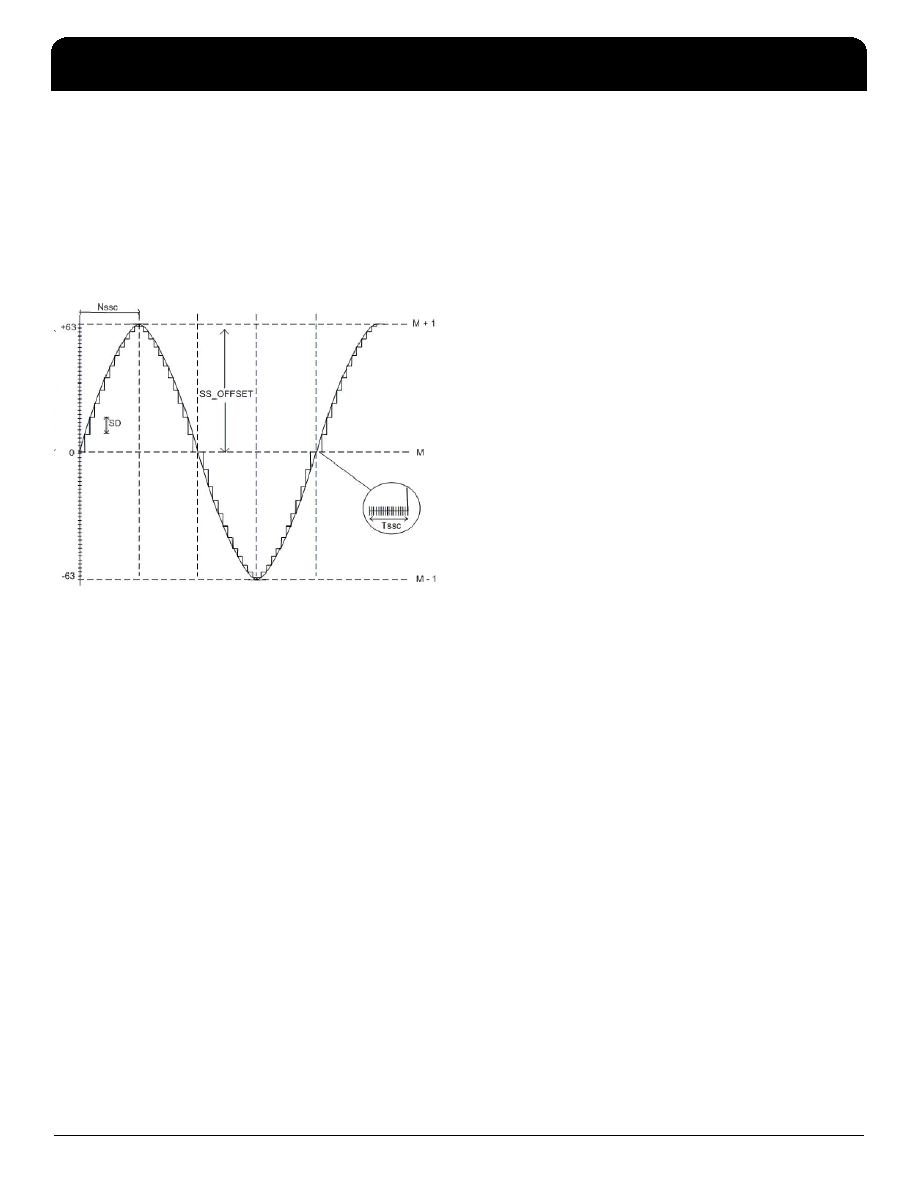

Waveform starts with SS_OFFSET, SS_OFFSET + SDJ,

SS_OFFSET + SDJ+1, etc.

Spread Spectrum Using Sinusoidal Profile

Example

FIN = 25MHz, FOUT = 100MHz, Fssc = 33KHz with center

spread of ±2%. Find the necessary spread spectrum

register settings.

Since the spread is center, the SS_OFFSET can be set to

'0'. Solve for the nominal M value; keep in mind that the

nominal M should be chosen to maximize

the VCO. Start with D = 1, using Eq.6 and Eq.7.

MNOM = 1200MHz / 25MHz = 48

Using Eq.4, we arbitrarily choose N = 22, A = 3. Now that we

have the nominal M value, we can determine TSSC and

NSSC by using Eq.8.

Nssc * Tssc = 25MHz / (33KHz * 4) = 190

However, using Eq. 2 and Eq.3, we find that the closest

value is when TSSC = 14 and NSSC = 6. Keep in mind to

maximize the number of samples used

to enhance the profile of the spread spectrum waveform.

Tssc = 14 + 2 = 16

Nssc = 6 * 2 = 12

Nssc * Tssc = 192

Use Eq.10 to determine the value of the

sigma-delta-encoded samples.

±2% =

(ΣΔ * 100)/(64 * 48)

ΣΔ = 61.4

Either round up or down to the nearest integer value.

Therefore, we end up with 61 or 62 for sigma-delta-encoded

samples. Since the sigma-delta-encoded samples must not

exceed 63 with SS_OFFSET set to '0', 61 or 62 is well within

the limits. It is the discretion of the user to define the shape

of the profile that is better suited for the intended application.

Using Eq. 9 again, the actual spread for the

sigma-delta-encoded samples of 56 and 57 are ±1.99% and

±2.02%, respectively.

Use Eq.10 to determine if the X2 bit needs to be set;

Amplitude = 48 * (1.99 or 2.02) / 100/2 = 0.48 < 1

Therefore, the X2 = '0 '. The dither bit is left to the discretion

of the user.

The example above was of a center spread using spread

spectrum. For down spread, the nominal M value can be set

one integer value lower to 47.

Note that the IDT5V49EE702 should not be programmed

with TSSC > '0', SS_OFFSET = '0', and SD = '0' in order to

prevent an unstable state in the modulator.

The PLL loop bandwidth must be at least 10x the

modulation frequency along with higher damping (larger

ωuz) to prevent the spread spectrum from being filtered and

reduce extraneous noise. Refer to the LOOP FILTER

section for more detail on

ωuz. The A[3:0] must be used for

spread spectrum, even if the total multiplier value is an even

integer.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT5V49EE502NLGI | IC PLL CLK GEN 200MHZ 24VQFN |

| ICS87021AMILF | IC CLK GENERATOR /1 /2 8-SOIC |

| MC10EP57MNTXG | IC MUX ECL DIFF 4:1 3.3/5 20-QFN |

| X9317WS8I-2.7 | IC DIGITAL POT 10K 100TP 8SOIC |

| X9317WS8I | IC DIGITAL POT 10K 100TP 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT5V49EE702NDGI8 | 功能描述:IC PLL CLK GEN 200MHZ 28VQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5V49EE703NDGI | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK GENERATOR |

| IDT5V49EE703NDGI8 | 制造商:Integrated Device Technology Inc 功能描述:IC CLK GEN EEPROM PROGR 28QFN |

| IDT5V49EE704NDGI | 功能描述:IC PLL CLK GEN 200MHZ 28VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| IDT5V49EE704NDGI8 | 功能描述:IC PLL CLK GEN 200MHZ 28VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。