- 您现在的位置:买卖IC网 > PDF目录9149 > IDT5V49EE702NDGI (IDT, Integrated Device Technology Inc)IC PLL CLK GEN 200MHZ 28VQFN PDF资料下载

参数资料

| 型号: | IDT5V49EE702NDGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 4/34页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLK GEN 200MHZ 28VQFN |

| 产品培训模块: | VersaClock™ III Programmable Clocks |

| 特色产品: | VersaClock III Timing Devices |

| 标准包装: | 75 |

| 系列: | VersaClock™ III |

| 类型: | 时钟发生器,多路复用器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVTTL,晶体 |

| 输出: | HCSL,LVCMOS,LVDS,LVPECL,LVTTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:7 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 500MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-VFQFN 裸露焊盘 |

| 供应商设备封装: | 28-VFQFPN(4x4) |

| 包装: | 管件 |

| 其它名称: | 800-1918 IDT5V49EE702DLGI |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

IDT5V49EE702

EEPROM PROGRAMMABLE CLOCK GENERATOR

CLOCK SYNTHESIZER

IDT EEPROM PROGRAMMABLE CLOCK GENERATOR

12

IDT5V49EE702

REV M 092412

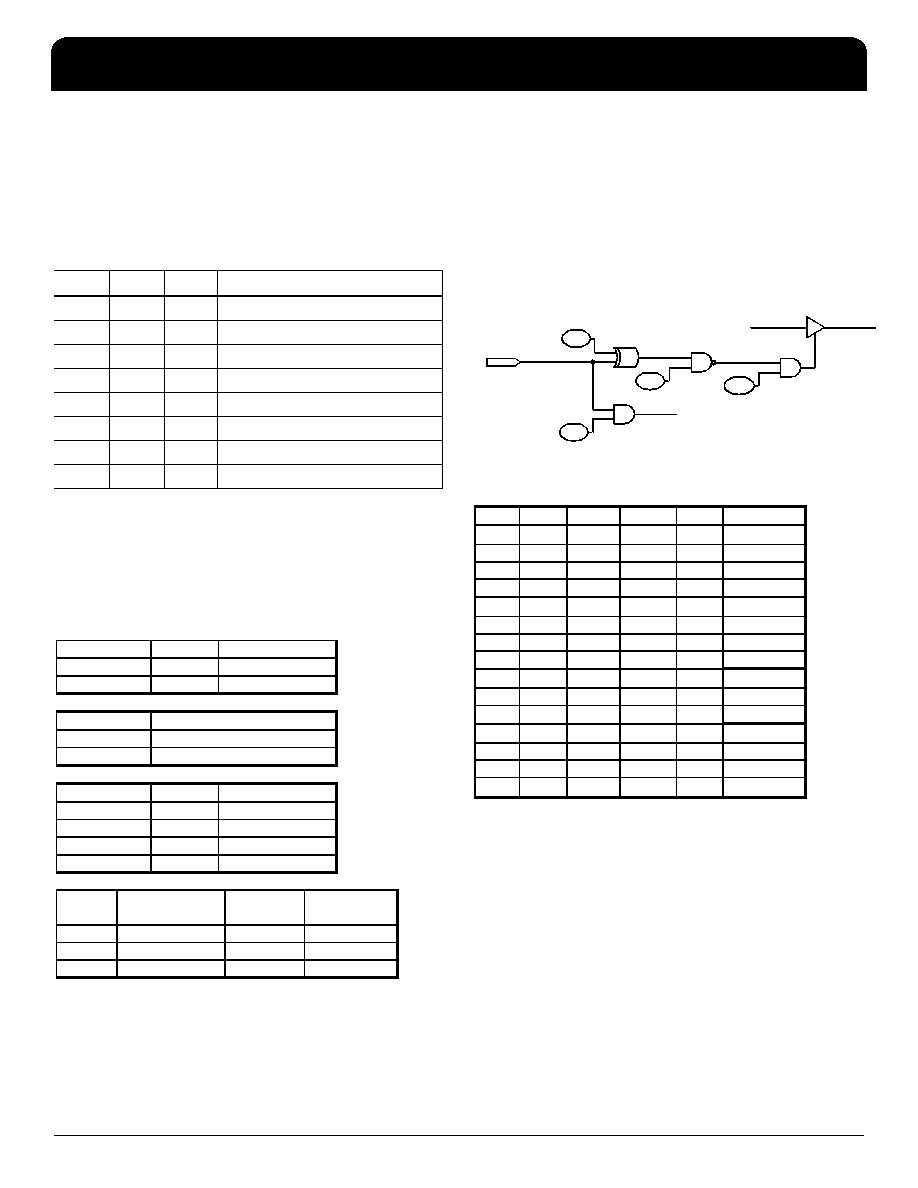

SEL[2:0] Function

The IDT5V49EE702 can support up to six unique

configurations. Users may pre-programmed all these

configurations, and select the configurations using SEL[2:0]

pins. Alternatively, users may use I2C interface to configure

these registers on-the-fly.

Crystal/Clock Selection

XTCLKSEL bit is used to bypass a crystal oscillator circuit

when external clock source is used.

PRIMSRC bit is used to select a primary clock from

XIN/REF and CLKIN.

SD/OE Pin Function

The polarity of the SD/OE signal pin can be programmed to

be either active HIGH or LOW with the SP bit (0x02). When

SP is “0” (default), the pin becomes active LOW and when

SP is “1”, the pin becomes active HIGH. The SD/OE pin can

be configured as either to shutdown the PLLs or to

enable/disable the outputs.

Configuration OUTx IO Standard

Users can configure the individual output IO standard from

a specified 1.8V to 3.3V power supplies. Each output can

support 1.8V to 3.3V LVTTL. Each output pair can support

LVDS, LVPECL or HCSL from the specified 3.3V power

supply. OUT0 can only be 3.3V single-ended output.

SEL2

SEL1

SEL0

Configuration Selections

0

Select CONFIG0

0

1

Select CONFIG1

0

1

0

Select CONFIG2

0

1

Select CONFIG3

1

0

Select CONFIG4

1

0

1

Select CONFIG5

1

0

Reserved (Do not use)

1

Reserved (Do not use)

PRIMSRC bit

Primary

Secondary

0XIN/REF

CLKIN

1

CLKIN

XIN/REF

CLKSEL input

0

1

CLKSEL

PRIMSRC Reference Clock

0

XIN/REF

01

CLKIN

10

CLKIN

1

XIN/REF

Clock Source

Primary Clock Source

Secondary Clock Source

SMx[1:0] Swithcing Mode

Primary to

Secondary

Secondary to

Primary

0x

Manual

No

10

Auto

Yes

No

11

Auto-Revertive

Yes

OUTn

OS

OE

SP

SD/OE Input

SH

Global Shutdown

Truth Table

SH bit SP bit OSn bit OEn bit SD/OE

OUTn

0

x

High-Z

2

0

1

0

x

Enabled

0

1

0

Enabled

0

1

Suspended

0

1

0

x

High-Z

2

0

1

0

x

Enabled

0

1

0

Suspended

0

1

Enabled

1

0

x

0

High-Z

2

1

0

1

0

Enabled

1

0

1

0

Enabled

1

0

x

0

High-Z

2

1

0

Enabled

1

0

Suspended

1x

x

1

Suspended

1

Note 1 : Global Shutdown

Note 2 : Hi-Z regardless of OEM bits

相关PDF资料 |

PDF描述 |

|---|---|

| IDT5V49EE502NLGI | IC PLL CLK GEN 200MHZ 24VQFN |

| ICS87021AMILF | IC CLK GENERATOR /1 /2 8-SOIC |

| MC10EP57MNTXG | IC MUX ECL DIFF 4:1 3.3/5 20-QFN |

| X9317WS8I-2.7 | IC DIGITAL POT 10K 100TP 8SOIC |

| X9317WS8I | IC DIGITAL POT 10K 100TP 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT5V49EE702NDGI8 | 功能描述:IC PLL CLK GEN 200MHZ 28VQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5V49EE703NDGI | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK GENERATOR |

| IDT5V49EE703NDGI8 | 制造商:Integrated Device Technology Inc 功能描述:IC CLK GEN EEPROM PROGR 28QFN |

| IDT5V49EE704NDGI | 功能描述:IC PLL CLK GEN 200MHZ 28VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| IDT5V49EE704NDGI8 | 功能描述:IC PLL CLK GEN 200MHZ 28VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。