- 您现在的位置:买卖IC网 > PDF目录9898 > IDT72V2113L10PFI8 (IDT, Integrated Device Technology Inc)IC FIFO SUPERSYNCII 10NS 80-TQFP PDF资料下载

参数资料

| 型号: | IDT72V2113L10PFI8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 34/46页 |

| 文件大小: | 0K |

| 描述: | IC FIFO SUPERSYNCII 10NS 80-TQFP |

| 标准包装: | 750 |

| 系列: | 72V |

| 功能: | 同步 |

| 存储容量: | 4.7Mb(262k x 18) |

| 访问时间: | 10ns |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 80-LQFP |

| 供应商设备封装: | 80-TQFP(14x14) |

| 包装: | 带卷 (TR) |

| 其它名称: | 72V2113L10PFI8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页当前第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

4

IDT72V263/273/283/293/103/113 3.3V HIGH DENSITY SUPERSYNC IITM NARROW BUS FIFO

8K x 18, 16K x 9/18, 32K x 9/18, 64K x 9/18, 128K x 9/18, 256K x 9/18, 512K x9

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V2103/72V2113 3.3V HIGH DENSITY SUPERSYNC IITM NARROW BUS FIFO

131,072 x 18/262,144 x 9, 262,144 x 18/524,288 x 9

JUNE 1, 2010

not have to be asserted for accessing the first word. However, subsequent

words written to the FIFO do require a LOW on

REN for access. The state of

the FWFT/SI input during Master Reset determines the timing mode in use.

For applications requiring more data storage capacity than a single FIFO

canprovide,theFWFTtimingmodepermitsdepthexpansionbychainingFIFOs

in series (i.e. the data outputs of one FIFO are connected to the corresponding

data inputs of the next). No external logic is required.

These FIFOs have five flag pins,

EF/OR (Empty Flag or Output Ready),

FF/IR (Full Flag or Input Ready), HF (Half-full Flag), PAE (Programmable

Almost-Emptyflag)and

PAF(ProgrammableAlmost-Fullflag).TheEFandFF

functions are selected in IDT Standard mode. The

IR and OR functions are

selected in FWFT mode.

HF, PAE and PAF are always available for use,

irrespective of timing mode.

PAE and PAFcanbeprogrammedindependentlytoswitchatanypointin

memory.Programmableoffsetsdeterminetheflagswitchingthresholdandcan

beloadedbytwomethods:parallelorserial.Eightdefaultoffsetsettingsarealso

provided, so that

PAEcanbesettoswitchatapredefinednumberoflocations

from the empty boundary and the

PAF threshold can also be set at similar

predefinedvaluesfromthefullboundary.Thedefaultoffsetvaluesaresetduring

Master Reset by the state of the FSEL0, FSEL1, and

LD pins.

Forserialprogramming,

SENtogetherwithLDoneachrisingedgeofWCLK,

are used to load the offset registers via the Serial Input (SI). For parallel

programming,

WEN togetherwithLD oneachrisingedgeofWCLK,areused

to load the offset registers via Dn.

REN together with LD on each rising edge

ofRCLKcanbeusedtoreadtheoffsetsinparallelfromQnregardlessofwhether

serial or parallel offset loading has been selected.

During Master Reset (

MRS)thefollowingeventsoccur:thereadandwrite

pointers are set to the first location of the FIFO. The FWFT pin selects IDT

Standard mode or FWFT mode.

The Partial Reset (

PRS) also sets the read and write pointers to the first

location of the memory. However, the timing mode, programmable flag

programmingmethod,anddefaultorprogrammedoffsetsettingsexistingbefore

PartialResetremainunchanged.Theflagsareupdatedaccordingtothetiming

modeandoffsetsineffect.

PRSisusefulforresettingadeviceinmid-operation,

when reprogramming programmable flags would be undesirable.

Itisalsopossibletoselectthetimingmodeofthe

PAE(ProgrammableAlmost-

Empty flag) and

PAF (Programmable Almost-Full flag) outputs. The timing

modes can be set to be either asynchronous or synchronous for the

PAE and

PAFflags.

If asynchronous

PAE/PAF configuration is selected, the PAE is asserted

LOWontheLOW-to-HIGHtransitionofRCLK.

PAEisresettoHIGHontheLOW-

DESCRIPTION (CONTINUED)

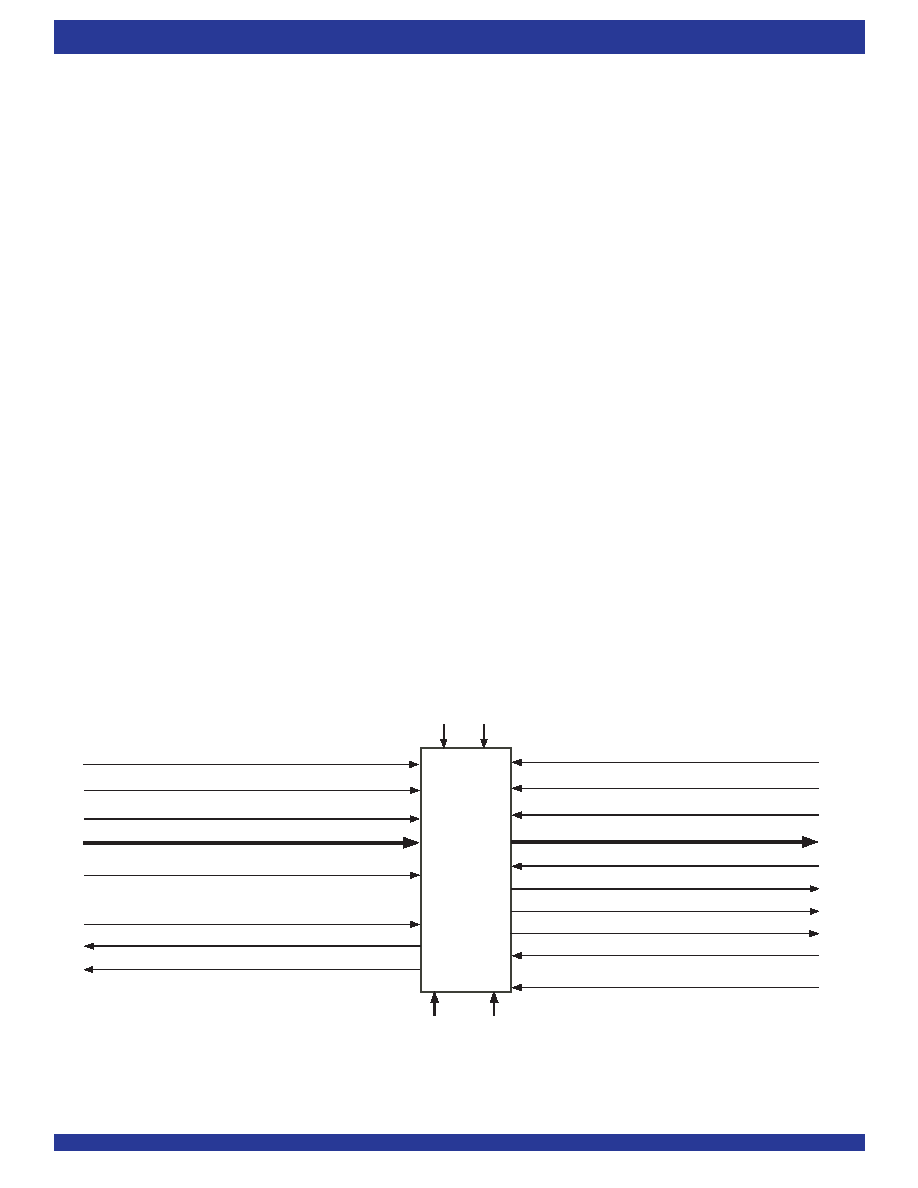

(x9 or x18) DATA OUT (Q0 - Qn)

(x9 or x18) DATA IN (D0 - Dn)

MASTER RESET (MRS)

READ CLOCK (RCLK/RD*)

READ ENABLE (REN)

OUTPUT ENABLE (OE)

EMPTY FLAG/OUTPUT READY (EF/OR)

PROGRAMMABLE ALMOST-EMPTY (PAE)

WRITE CLOCK (WCLK/WR*)

WRITE ENABLE (WEN)

LOAD (LD)

FULL FLAG/INPUT READY (FF/IR)

PROGRAMMABLE ALMOST-FULL (PAF)

IDT

72V2103

72V2113

PARTIAL RESET (PRS)

FIRST WORD FALL THROUGH/SERIAL

INPUT (FWFT/SI)

RETRANSMIT (RT)

6119 drw03

HALF-FULL FLAG (HF)

SERIAL ENABLE(SEN)

INPUT WIDTH

(IW)

OUTPUT WIDTH

(OW)

BIG-ENDIAN/LITTLE-ENDIAN (BE)

INTERSPERSED/

NON-INTERSPERSED PARITY (IP)

Figure 1. Single Device Configuration Signal Flow Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| MAX1416EWE+ | IC ADC 16BIT DELTA SIGMA 16-SOIC |

| IDT72T36105L5BB | IC FIFO 131X18 5NS 240BGA |

| MAX111ACAP+T | IC ADC 14BIT 2CH 5V 20-SSOP |

| IDT72T18105L5BB | IC FIFO 131X18 2.5V 5NS 240BGA |

| D38999/24WF32SB | CONN RCPT 32POS JAM NUT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V2113L15PF | 功能描述:IC FIFO SUPERSYNCII 15NS 80-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V2113L15PF8 | 功能描述:IC FIFO SUPERSYNCII 15NS 80-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V2113L6BC | 功能描述:IC FIFO SUPERSYNCII 6NS 100-BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V2113L6PF | 功能描述:IC FIFO SUPERSYNCII 6NS 80-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V2113L6PF8 | 功能描述:IC FIFO SUPERSYNCII 6NS 80-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

发布紧急采购,3分钟左右您将得到回复。