- 您现在的位置:买卖IC网 > PDF目录4020 > IDT79RC32V333-100DHI (IDT, Integrated Device Technology Inc)IC PROC 32BIT CPU 100MHZ 208-QFP PDF资料下载

参数资料

| 型号: | IDT79RC32V333-100DHI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 30/30页 |

| 文件大小: | 0K |

| 描述: | IC PROC 32BIT CPU 100MHZ 208-QFP |

| 产品变化通告: | Product Discontinuation 07/Dec/2009 |

| 标准包装: | 24 |

| 系列: | Interprise™ |

| 处理器类型: | RISC 32-位 |

| 速度: | 100MHz |

| 电压: | 3.3V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-BFQFP |

| 供应商设备封装: | 208-PQFP(28x28) |

| 包装: | 托盘 |

| 其它名称: | 79RC32V333-100DHI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页

9 of 30

May 4, 2004

IDT 79RC32333

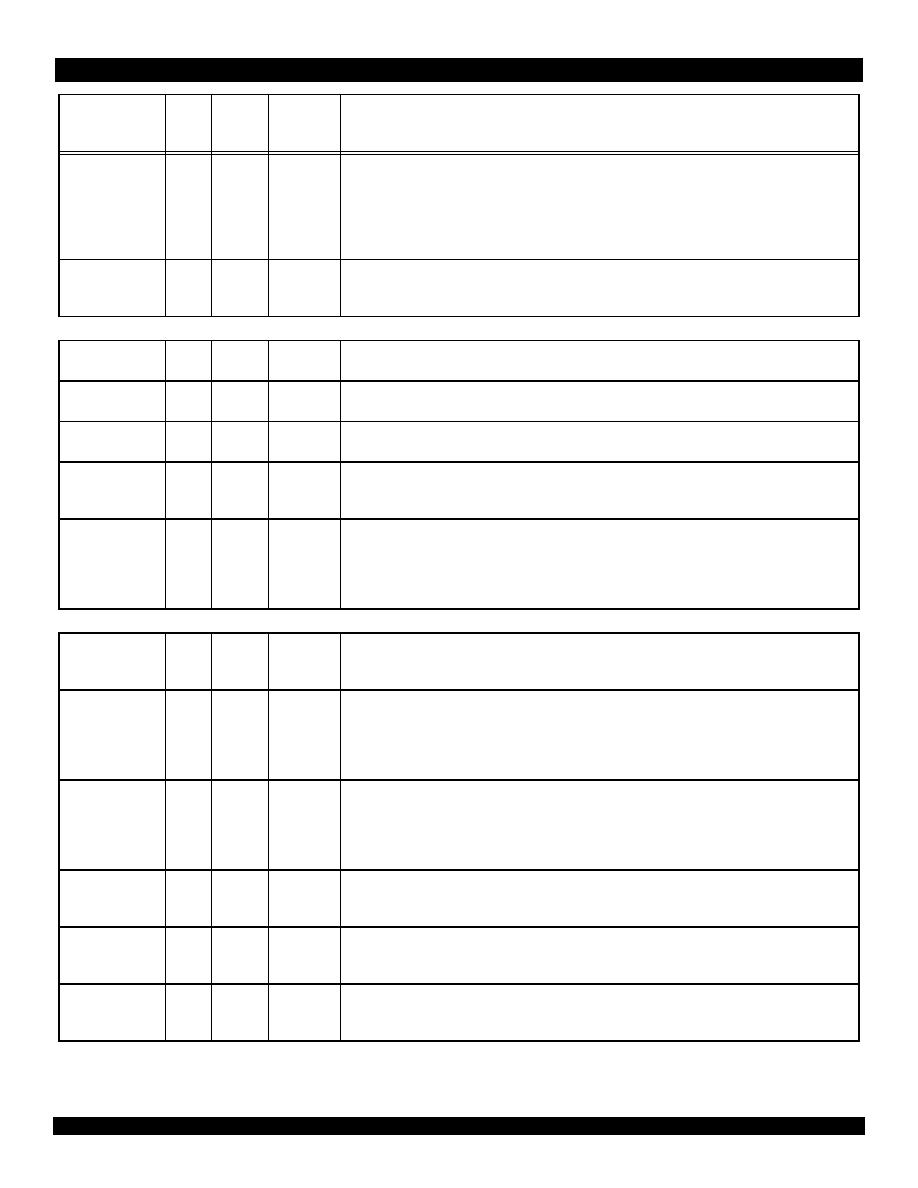

spi_sck

I/O

L

Low

SPI Clock

Serial mode: Output pin for Serial Clock.

In PCI satellite mode, acts as an Output pin for Serial Clock for loading PCI Configuration Registers in the

RC323333 Reset Initialization Vector PCI boot mode.

1st Alternate function: PIO[5]. Defaults to the output direction at reset time.

2nd Alternate function: pci_eeprom_sk.

spi_ss_n

I/O

H

Low

SPI Chip Select

Output pin selecting the serial protocol device as opposed to the PCI satellite mode EEPROM device.

Alternate function: PIO[4]. Defaults to the output direction at reset time.

CPU Core Specific Signals

cpu_nmi_n

Input

—

CPU Non-Maskable Interrupt Requires an external pull-up.

This interrupt input is active low to the CPU.

cpu_masterclk

Input

—

CPU Master System Clock

Provides the basic system clock.

cpu_int_n[1:0]

Input

—

CPU Interrupt Requires an external pull-up.

These interrupt inputs are active low to the CPU.

cpu_coldreset_n

Input

L

—

CPU Cold Reset

This active-low signal is asserted to the RC32333 after

Vcc becomes valid on the initial power-up. The

Reset initialization vectors for the RC32333 are latched by cold reset.

cpu_dt_r_n

Output

Z

—

CPU Direction Transmit/Receive

This active-low signal controls the DT/R pin of an optional FCT245 transceiver bank. It is asserted during

read operations.

1st Alternate function: mem_245_dt_r_n.

2nd Alternate function: sdram_245_dt_r_n.

JTAG Interface Signals

jtag_tck

Input

—

JTAG Test Clock Requires an external pull-down.

An input test clock used to shift into or out of the Boundary-Scan register cells. jtag_tck is independent of

the system and the processor clock with nominal 50% duty cycle.

jtag_tdi,

ejtag_dint_n

Input

—

JTAG Test Data In Requires an external pull-up.

On the rising edge of jtag_tck, serial input data are shifted into either the Instruction or Data register,

depending on the TAP controller state. During Real Mode, this input is used as an interrupt line to stop the

debug unit from Real Time mode and return the debug unit back to Run Time Mode (standard JTAG).

This pin is also used as the ejtag_dint_n signal in the EJTAG mode.

jtag_tdo,

ejtag_tpc

Output

Z

High

JTAG Test Data Out

The jtag_tdo is serial data shifted out from instruction or data register on the falling edge of jtag_tck.

When no data is shifted out, the jtag_tdo is tri-stated. During Real Time Mode, this signal provides a non-

sequential program counter at the processor clock or at a division of processor clock. This pin is also

used as the ejtag_tpc signal in the EJTAG mode.

jtag_tms

Input

—

JTAG Test Mode Select Requires an external pull-up.

The logic signal received at the jtag_tms input is decoded by the TAP controller to control test operation.

jtag_tms is sampled on the rising edge of the jtag_tck.

jtag_trst_n

Input

L

—

JTAG Test Reset

When neither JTAG nor EJTAG are being used, jtag_trst_n must be driven low (pulled down) or the

jtag_tms/ejtag_tms signals must be pulled up and jtag_clk actively clocked.

ejtag_dclk

Output

Z

—

EJTAG Test Clock

Processor Clock. During Real Time Mode, this signal is used to capture address and data from the

ejtag_tpc signal at the processor clock speed or any division of the internal pipeline.

Name

Type

Reset

State

Status

Drive

Strength

Capability

Description

Table 1 Pin Descriptions (Part 5 of 6)

相关PDF资料 |

PDF描述 |

|---|---|

| IDT79RC32V333-100DHG | IC PROC 32BIT CPU 100MHZ 208-QFP |

| AMM18DREN | CONN EDGECARD 36POS .156 EYELET |

| 046288020000846+ | CONN FFC/FPC 20POS .5MM R/A SMD |

| AMM18DREH | CONN EDGECARD 36POS .156 EYELET |

| FMC31DRES-S93 | CONN EDGECARD 62POS .100 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT79RC32V333-133DH | 功能描述:IC PROC 32BIT CPU 133MHZ 208-QFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:Interprise™ 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

| IDT79RC32V333-133DHG | 功能描述:IC PROC 32BIT CPU 133MHZ 208-QFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:Interprise™ 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

| IDT79RC32V333-133DHI | 功能描述:IC PROC 32BIT CPU 133MHZ 208-QFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:Interprise™ 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

| IDT79RC32V333-150DH | 功能描述:IC PROC 32BIT CPU 150MHZ 208-QFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:Interprise™ 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

| IDT79RC32V333-150DHG | 功能描述:IC PROC 32BIT CPU 150MHZ 208-QFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:Interprise™ 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。