- 您现在的位置:买卖IC网 > PDF目录377488 > IDT82V2608BB (INTEGRATED DEVICE TECHNOLOGY INC) INVERSE MULTIPLEXING FOR ATM PDF资料下载

参数资料

| 型号: | IDT82V2608BB |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 数字传输电路 |

| 英文描述: | INVERSE MULTIPLEXING FOR ATM |

| 中文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA208 |

| 封装: | PLASTIC, BGA-208 |

| 文件页数: | 13/98页 |

| 文件大小: | 398K |

| 代理商: | IDT82V2608BB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页

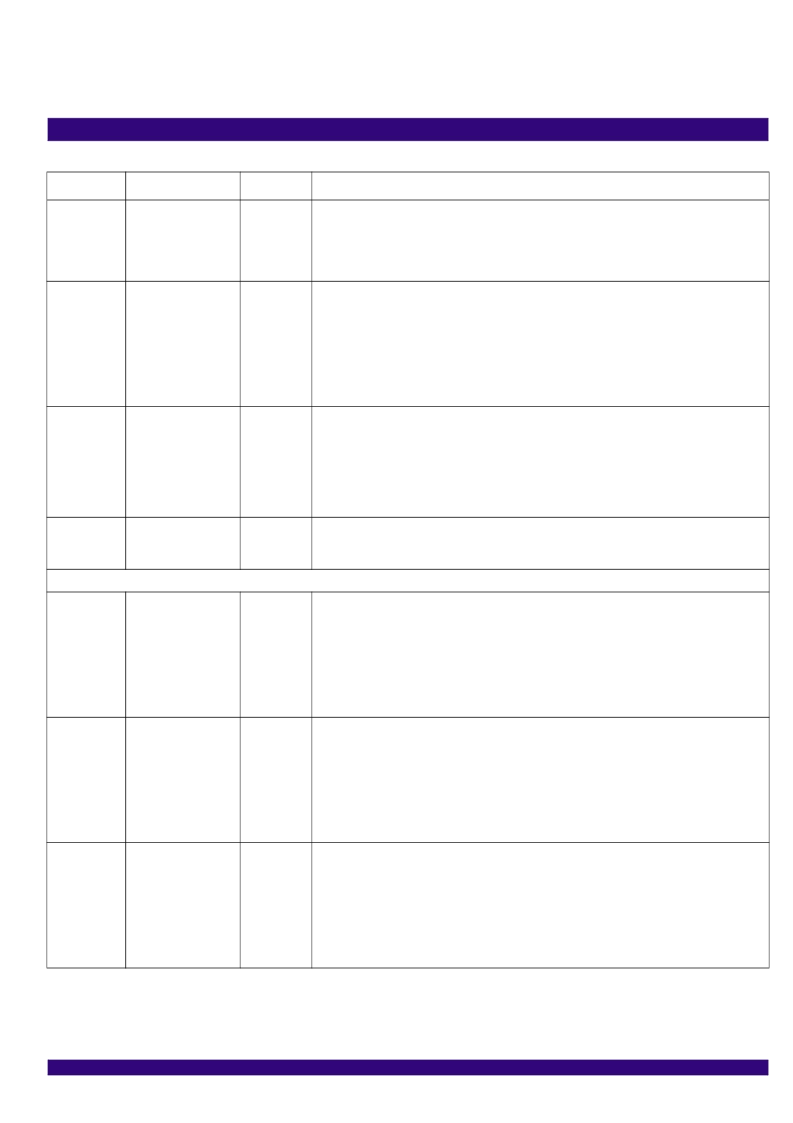

PIN DESCRIPTION

13

December 4, 2006

IDT82V2608

Inverse Multiplexing for ATM

RxAddr4

RxAddr3

RxAddr2

RxAddr1

RxAddr0

C14

C15

C16

D13

D14

I

RxAddr[4:0]: Utopia Receive Address

Utopia receive port address driven fromthe ATMlayer to poll and select an appropriate port.

The RxAddr[4:0] input bus are sampled on the rising edge of RxClk.

RxData7

RxData6

RxData5

RxData4

RxData3

RxData2

RxData1

RxData0

A15

B14

A14

C13

B13

A13

D12

C12

High-Z

O

RxData[7:0]: Utopia Receive Data

Utopia 8-bit data bus driven fromthe IDT82V2608 to the ATMlayer.

The RxData[7:0] output bus are updated on the rising edge of RxClk.

RxClav

B16

High-Z

O

RxClav: Utopia Receive Cell Available

Utopia cell available signal. A polled port drives RxClav only during each cycle following one with its

address on the RxAddr lines. The polled port asserts RxClav high to indicate its corresponding FIFO

has a complete cell available for transfer to the ATMlayer, otherwise it deasserts the signal.

The RxClav output is updated on the rising edge of RxClk.

Note:

This pin requires a pull-down resistor.

RxSOC

B15

High-Z

O

RxSOC: Utopia Receive Start of Cell

Utopia start of cell pulse. It will be driven high when RxData[7:0] contain the first valid byte of a cell.

The RxSOC input is updated on the rising edge of RxClk.

T1/E1 Line Interface

TSD8

TSD7

TSD6

TSD5

TSD4

TSD3

TSD2

TSD1

R3

R4

R5

R6

R7

R8

R9

R10

O

TSDn: Transmit Side Data Output

TSDn contains the transmt data for the n-th link.

The TSDn output is updated on the rising edge of TSCKn or TSCCK if common clock is used.

TSCK8

TSCK7

TSCK6

TSCK5

TSCK4

TSCK3

TSCK2

TSCK1

T3

T4

T5

T6

T7

T8

P9

P10

I

TSCKn: Transmit Side Clock

TSCKn contains the transmt clock for the n-th link.

Note:

If unused, TSCKn should be connected to ground.

TSF8

TSF7

TSF6

TSF5

TSF4

TSF3

TSF2

TSF1

P4

P5

P6

P7

P8

T9

T10

T11

I

TSFn: Transmit Side Frame pulse

TSFn is used to delineate each frame for the n-th link.

The TSFn input is sampled on the falling edge of TSCKn or TSCCK if common clock is used.

Note:

If unused, TSFn should be connected to ground.

Table-1 Pin Description (Continued)

Name

Pin Number

Input/Output

Description

相关PDF资料 |

PDF描述 |

|---|---|

| IDT82V2608 | INVERSE MULTIPLEXING FOR ATM |

| IDT82V3001A | WAN PLL WITH SINGLE REFERENCE INPUT |

| IDT82V3001APV | WAN PLL WITH SINGLE REFERENCE INPUT |

| IDT82V3002A | WAN PLL WITH DUAL REFERENCE INPUTS |

| IDT82V3002APV | WAN PLL WITH DUAL REFERENCE INPUTS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V2608BBG | 功能描述:IC INVERSE MUX 8CH ATM 208-BGA RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 标准包装:3,000 系列:- 应用:PDA,便携式音频/视频,智能电话 接口:I²C,2 线串口 电源电压:1.65 V ~ 3.6 V 封装/外壳:24-WQFN 裸露焊盘 供应商设备封装:24-QFN 裸露焊盘(4x4) 包装:带卷 (TR) 安装类型:表面贴装 产品目录页面:1015 (CN2011-ZH PDF) 其它名称:296-25223-2 |

| IDT82V2616 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:INVERSE MULTIPLEXING FOR ATM |

| IDT82V2616BB | 功能描述:IC INVERSE MUX 16CH ATM 272-PBGA RoHS:否 类别:集成电路 (IC) >> 接口 - 专用 系列:- 标准包装:3,000 系列:- 应用:PDA,便携式音频/视频,智能电话 接口:I²C,2 线串口 电源电压:1.65 V ~ 3.6 V 封装/外壳:24-WQFN 裸露焊盘 供应商设备封装:24-QFN 裸露焊盘(4x4) 包装:带卷 (TR) 安装类型:表面贴装 产品目录页面:1015 (CN2011-ZH PDF) 其它名称:296-25223-2 |

| IDT82V2616BBG | 功能描述:IC INVERSE MUX 16CH ATM 272-PBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 标准包装:3,000 系列:- 应用:PDA,便携式音频/视频,智能电话 接口:I²C,2 线串口 电源电压:1.65 V ~ 3.6 V 封装/外壳:24-WQFN 裸露焊盘 供应商设备封装:24-QFN 裸露焊盘(4x4) 包装:带卷 (TR) 安装类型:表面贴装 产品目录页面:1015 (CN2011-ZH PDF) 其它名称:296-25223-2 |

| IDT82V3001A | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL WITH SINGLE REFERENCE INPUT |

发布紧急采购,3分钟左右您将得到回复。