- 您现在的位置:买卖IC网 > PDF目录377488 > IDT82V3255TF (INTEGRATED DEVICE TECHNOLOGY INC) WAN PLL PDF资料下载

参数资料

| 型号: | IDT82V3255TF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 通信及网络 |

| 英文描述: | WAN PLL |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP64 |

| 封装: | TQFP-64 |

| 文件页数: | 46/127页 |

| 文件大小: | 868K |

| 代理商: | IDT82V3255TF |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页

IDT82V3255

WAN PLL

Programming Information

46

June 19, 2006

6

PROGRAMMING INFORMATION

After reset, all the registers are set to their default values. The regis-

ters are read or written via the microprocessor interface.

Before

PROTECTION_CNFG is recommended to be confirmed to make sure

whether the write operation is enabled. The device provides 3 register

protection modes:

Protected mode: no other registers can be written except register

PROTECTION_CNFG itself;

Fully Unprotected mode: all the writable registers can be written;

Single Unprotected mode: one more register can be written

besides register PROTECTION_CNFG. After write operation

(not including writing a ‘1’ to clear a bit to ‘0’), the device auto-

matically switches to Protected mode.

any

write

operation,

the

value

in

register

Writing ‘0’ to the registers will take no effect if the registers are

cleared by writing ‘1’.

T0 and T4 paths share some registers, whose addresses are 27H,

28H, 2AH, 4EH, 4FH, 5AH, 5BH, 62H ~ 64H, 68H and 69H. The names

of shared registers are marked with a *. Before register read/write oper-

ation, register T4_T0_REG_SEL_CNFG is recommended to be con-

firmed to make sure whether the register operation is available for T0 or

T4 path.

The access of the Multi-word Registers is different from that of the

Single-word Registers. Take the registers (04H, 05H and 06H) for an

example, the write operation for the Multi-word Registers follows a fixed

sequence. The register (04H) is configured first and the register (06H) is

configured last. The three registers are configured continuously and

should not be interrupted by any operation. The crystal calibration con-

figuration will take effect after all the three registers are configured. Dur-

ing read operation, the register (04H) is read first and the register (06H)

is read last. The crystal calibration reading should be continuous and not

be interrupted by any operation.

Certain bit locations within the device register map are designated as

Reserved. To ensure proper and predictable operation, bits designated

as Reserved should not be written by the users. In addition, their value

should be masked out from any testing or error detection methods that

are implemented.

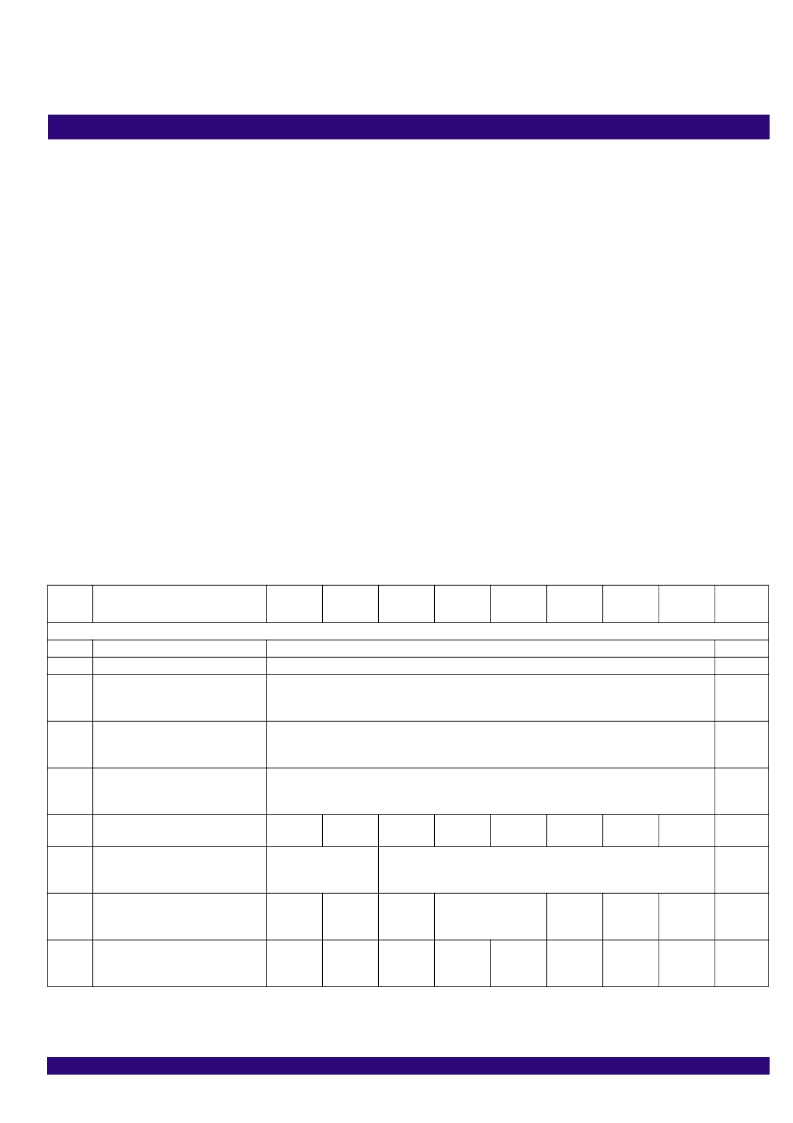

6.1

REGISTER MAP

Table 34

is the map of all the registers, sorted in an ascending order

of their addresses.

Table 34: Register List and Map

Address

(Hex)

Register Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Reference

Page

Global Control Registers

00

01

ID[7:0] - Device ID 1

ID[15:8] - Device ID 2

NOMINAL_FREQ[7:0]_CNFG - Crys-

tal Oscillator Frequency Offset Calibra-

tion Configuration 1

NOMINAL_FREQ[15:8]_CNFG - Crys-

tal Oscillator Frequency Offset Calibra-

tion Configuration 2

NOMINAL_FREQ[23:16]_CNFG

Crystal Oscillator Frequency Offset

Calibration Configuration 3

T4_T0_REG_SEL_CNFG - T0 / T4

Registers Selection Configuration

PHASE_ALARM_TIME_OUT_CNFG -

Phase Lock Alarm Time-Out Configu-

ration

ID[7:0]

ID[15:8]

P 51

P 51

04

NOMINAL_FREQ_VALUE[7:0]

P 52

05

NOMINAL_FREQ_VALUE[15:8]

P 52

06

-

NOMINAL_FREQ_VALUE[23:16]

P 52

07

-

-

-

T4_T0_SE

L

-

-

-

-

P 53

08

MULTI_FACTOR[1:0]

TIME_OUT_VALUE[5:0]

P 53

09

INPUT_MODE_CNFG - Input Mode

Configuration

AUTO_EX

T_SYNC_

EN

EXT_SYN

C_EN

PH_ALAR

M_TIMEO

UT

SYNC_FREQ[1:0]

IN_SONET

_SDH

-

REVERTIV

E_MODE

P 54

0A

DIFFERENTIAL_IN_OUT_OSCI_CNF

G - Differential Input / Output Port &

Master Clock Configuration

-

-

-

-

-

OSC_EDG

E

OUT1_PE

CL_LVDS

-

P 55

相关PDF资料 |

PDF描述 |

|---|---|

| IDT82V3255TFG | WAN PLL |

| IDT82V3280 | WAN PLL |

| IDT82V3280DQ | WAN PLL |

| IDT82V3280DQG | WAN PLL |

| IDT82V3280PF | WAN PLL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V3255TFBLANK | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL |

| IDT82V3255TFG | 功能描述:IC PLL WAN SMC STRATUM 3 64-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| IDT82V3255TFG8 | 功能描述:IC PLL WAN SMC STRATUM 3 64-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| IDT82V3255TFGBLANK | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL |

| IDT82V3280 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL |

发布紧急采购,3分钟左右您将得到回复。