- 您现在的位置:买卖IC网 > PDF目录1807 > IP1206TRPBF (International Rectifier)IC REG BUCK SYNC ADJ 30A/15A LGA PDF资料下载

参数资料

| 型号: | IP1206TRPBF |

| 厂商: | International Rectifier |

| 文件页数: | 11/30页 |

| 文件大小: | 0K |

| 描述: | IC REG BUCK SYNC ADJ 30A/15A LGA |

| 产品变化通告: | (EP) Parts Discontinuation 25/May/2012 |

| 标准包装: | 750 |

| 系列: | iPOWIR™ |

| 类型: | 降压(降压) |

| 输出类型: | 可调式 |

| 输出数: | 1 或 2 |

| 输出电压: | 0.8 V ~ 5.5 V |

| 输入电压: | 7.5 V ~ 14.5 V |

| PWM 型: | 电压模式 |

| 频率 - 开关: | 200kHz ~ 600kHz |

| 电流 - 输出: | 30A,15A |

| 同步整流器: | 是 |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 36-BFLGA |

| 包装: | 带卷 (TR) |

| 供应商设备封装: | 36-LGA(9.25x15.5) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

�� ��

��

��

��i� P1206PbF�

�Internal� Regulator�

�iP1206� features� an� on-board� regulator� capable� of�

�sourcing� current� up� to� 100mA.� This� integrated�

�regulator� can� be� used� to� generate� the� necessary�

�bias� voltage� for� drivers.� An� example� of� how� this�

�can� be� used� is� shown� in� Fig.� 25.� The� output� of�

�In� addition,� the� 180� o� out� of� phase� operation�

�contributes� to� input� current� cancellation.� This�

�results� in� a� much� smaller� input� capacitor� -� RMS�

�current� thereby� reducing� the� input� capacitor�

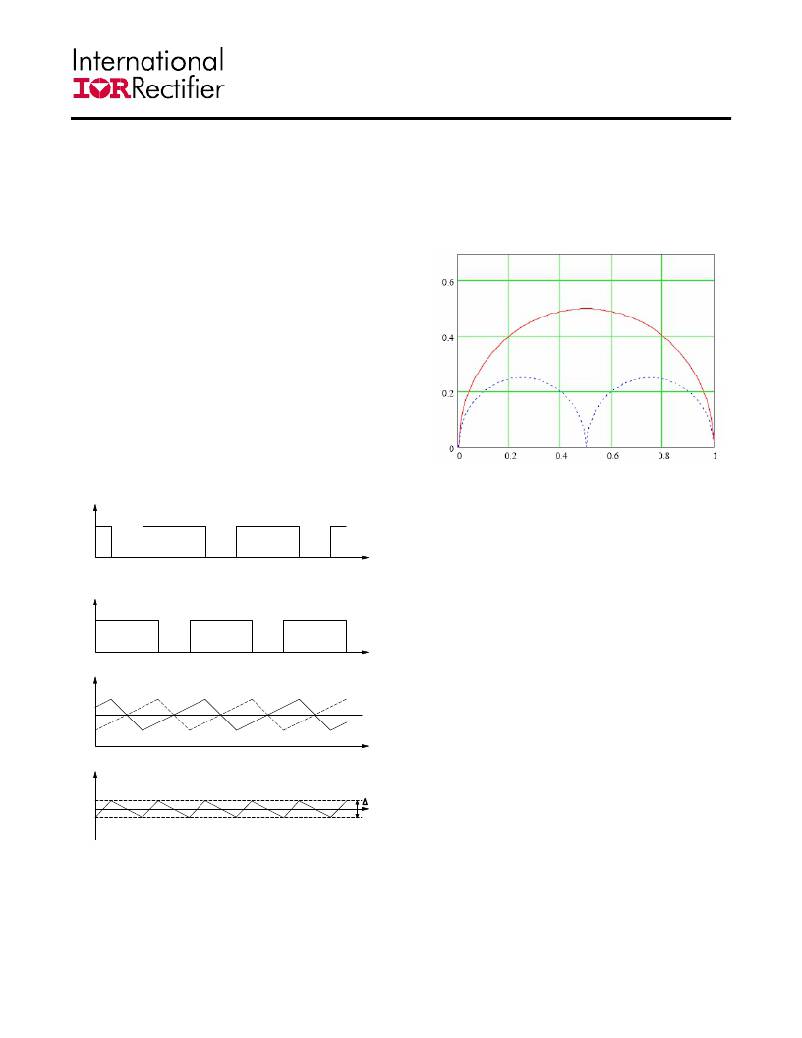

�quantity.� Fig.� 8� shows� the� equivalent� RMS�

�current.�

�the� regulator� is� protected� for� short� circuit� and�

�thermal� shutdown.�

�Single� Phase�

�Out-of-Phase� Operation�

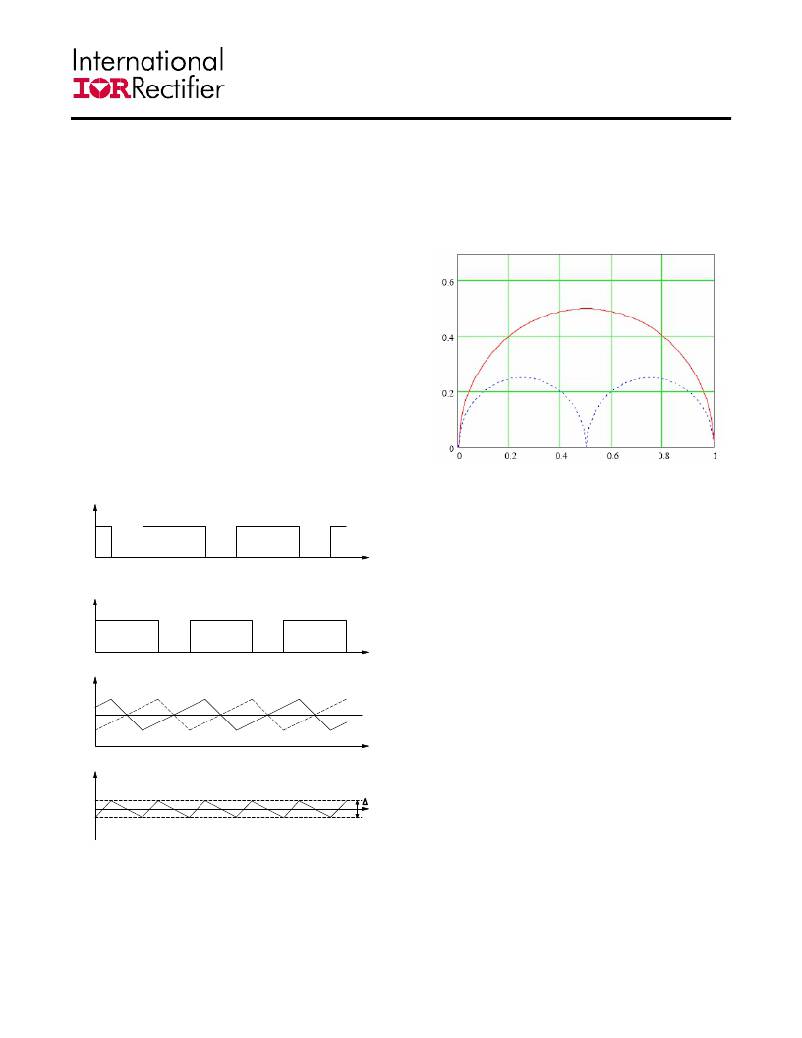

�The� iP1206� drives� its� two� output� stages� 180� o� out-�

�of-phase.� In� current� share� mode� (single� output),�

�the� two� inductor� ripple� currents� cancel� each� other�

�and� result� in� a� reduction� of� the� output� current�

�2� Phase�

�ripple� and� yield� a� smaller� output� capacitor� for� the�

�same� ripple� voltage� requirement.� Fig.� 7� shows�

�two� channels� inductor� current� and� the� resulting�

�voltage� ripple� at� output.�

�Duty� Cycle� (Vo/Vin)�

�HDRV1�

�Fig.� 8:� Input� RMS� value� vs.� Duty� Cycle�

�Mode� Selection�

�0�

�DT�

�T�

�The� iP1206� can� operate� as� a� dual� output�

�independently� regulated� buck� converter,� or� as� a�

�HDRV2�

�2� phase� single� output� buck� converter� (in� current�

�share� mode).� The� SS2� pin� is� used� for� mode�

�selection.� In� current� share� mode� this� pin� should�

�be� floating� and� in� dual� output� mode� a� soft� start�

�capacitor� must� be� connected� from� this� pin� to�

�ground� to� program� the� start� time� for� the� second�

�Ic�

�IL1�

�IL2�

�Io�

�output.�

�Independent� Mode�

�In� this� mode� the� iP1206� provides� control� to� two�

�independent� output� power� supplies� with� either�

�common� or� different� input� voltages.� The� output�

�voltage� of� each� individual� channel� is� set� and�

�controlled� by� the� output� of� the� error� amplifier,�

�which� is� the� amplified� error� signal� from� the�

�sensed� output� voltage� and� the� reference� voltage.�

�The� error� amplifier� output� voltage� is� compared� to�

�Fig.� 7:� Current� ripple� cancellation� for� output�

�the� ramp� signal� thus� generating� fixed� frequency�

�pulses� of� variable� duty-cycle,� (PWM)� which� are�

�applied� to� the� internal� MOSEFT� drivers.� Fig.� 25b�

�shows� a� typical� schematic� for� such� an�

�application.�

�www.irf.com�

�2/26/2008�

�11�

�相关PDF资料 |

PDF描述 |

|---|---|

| IP1827PBF | IC REG BUCK SYNC ADJ 25A LGA |

| IP1837PBF | IC REG BUCK SYNC ADJ 35A LGA |

| IP2001TRPBF | IC REG BUCK SYNC ADJ 20A 144BGA |

| IP2001TR | IC REG BUCK SYNC ADJ 20A 144BGA |

| IP2002TRPBF | IC REG BUCK SYNC ADJ 30A 144BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP120A | 制造商:SEME-LAB 制造商全称:Seme LAB 功能描述:1.5 AMP NEGATIVE VOLTAGE REGULATOR |

| IP120A-05 | 制造商:SEME-LAB 制造商全称:Seme LAB 功能描述:1.5 AMP NEGATIVE VOLTAGE REGULATOR |

| IP120A-12 | 制造商:SEME-LAB 制造商全称:Seme LAB 功能描述:1.5 AMP NEGATIVE VOLTAGE REGULATOR |

| IP120A-15 | 制造商:SEME-LAB 制造商全称:Seme LAB 功能描述:1.5 AMP NEGATIVE VOLTAGE REGULATOR |

| IP120AG-05 | 制造商:SEME-LAB 制造商全称:Seme LAB 功能描述:1.5 AMP NEGATIVE VOLTAGE REGULATOR |

发布紧急采购,3分钟左右您将得到回复。