- 您现在的位置:买卖IC网 > PDF目录176103 > ISD4003-08MSI (WINBOND ELECTRONICS CORP) 480 SEC, SPEECH SYNTHESIZER WITH RCDG, PDSO28 PDF资料下载

参数资料

| 型号: | ISD4003-08MSI |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | 音频合成 |

| 英文描述: | 480 SEC, SPEECH SYNTHESIZER WITH RCDG, PDSO28 |

| 封装: | 0.1200 INCH, PLASTIC, SOIC-28 |

| 文件页数: | 6/37页 |

| 文件大小: | 392K |

| 代理商: | ISD4003-08MSI |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

14

ATmega165A/PA/325A/PA/3250A/PA/645A/P/6450A/P [DATASHEET]

8285E–AVR–02/2013

SRAM Stack area where the Subroutine and Interrupt Stacks are located. A Stack PUSH command will decrease

the Stack Pointer.

The Stack in the data SRAM must be defined by the program before any subroutine calls are executed or interrupts

are enabled. Initial Stack Pointer value equals the last address of the internal SRAM and the Stack Pointer must be

set to point above start of the SRAM, see Figure 8-2 on page 19.

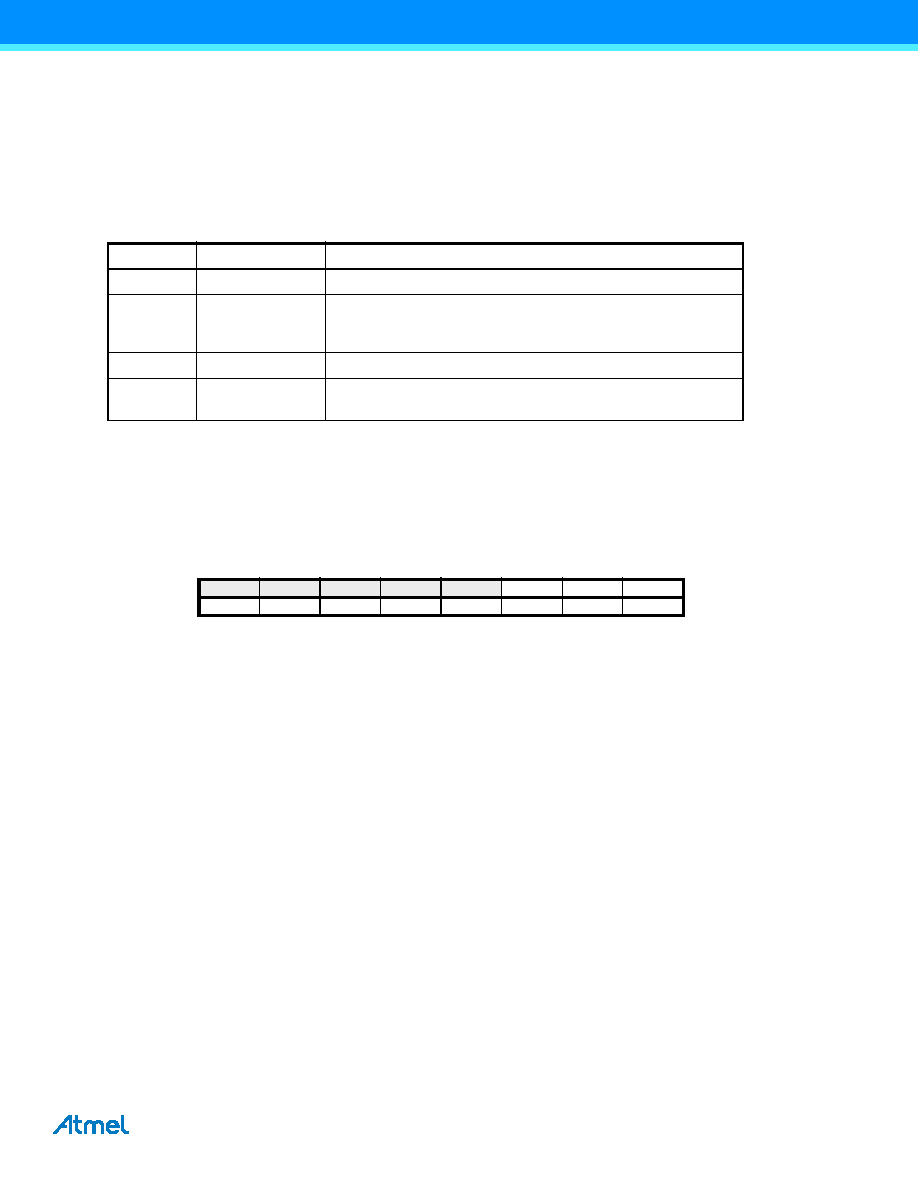

See Table 7-1 for Stack Pointer details.

The AVR Stack Pointer is implemented as two 8-bit registers in the I/O space. The number of bits actually used is

implementation dependent. Note that the data space in some implementations of the AVR architecture is so small

that only SPL is needed. In this case, the SPH Register will not be present.

7.6.1

SPH and SPL – Stack Pointer

7.7

Instruction execution timing

This section describes the general access timing concepts for instruction execution. The AVR CPU is driven by the

CPU clock clk

CPU, directly generated from the selected clock source for the chip. No internal clock division is used.

Figure 7-4 on page 15 shows the parallel instruction fetches and instruction executions enabled by the Harvard

architecture and the fast-access Register File concept. This is the basic pipelining concept to obtain up to 1 MIPS

per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per

power-unit.

Table 7-1.

Stack Pointer instructions.

Instruction

Stack pointer

Description

PUSH

Decremented by 1

Data is pushed onto the stack

CALL

ICALL

RCALL

Decremented by 2

Return address is pushed onto the stack with a subroutine call or

interrupt

POP

Incremented by 1

Data is popped from the stack

RET

RETI

Incremented by 2

Return address is popped from the stack with return from

subroutine or return from interrupt

Bit

151413121110

9

8

0x3E (0x5E)

–

SP10

SP9

SP8

SPH

0x3D (0x5D)

SP7

SP6

SP5

SP4

SP3

SP2

SP1

SP0

SPL

765

43210

Read/Write

R/W

Initial Value

000

00000

000

00000

相关PDF资料 |

PDF描述 |

|---|---|

| ISD4003-04MZD | 240 SEC, SPEECH SYNTHESIZER WITH RCDG, PBGA19 |

| ISD4003-04MZI | 240 SEC, SPEECH SYNTHESIZER WITH RCDG, PBGA19 |

| ISD4003-05MZD | 300 SEC, SPEECH SYNTHESIZER WITH RCDG, PBGA19 |

| ISD4003-05MZI | 300 SEC, SPEECH SYNTHESIZER WITH RCDG, PBGA19 |

| ISD4003-06MZD | 360 SEC, SPEECH SYNTHESIZER WITH RCDG, PBGA19 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISD4003-08MSIR | 功能描述:IC VOICE REC/PLAY 8MIN IN 28SOIC RoHS:否 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD4003 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000 |

| ISD4003-08MSY | 功能描述:IC VOICE REC/PLAY 8MIN 28-SOIC RoHS:是 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD4003 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000 |

| ISD4003-08MSYI | 功能描述:IC VOICE REC/PLAY 8MIN 28-SOIC RoHS:是 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD4003 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000 |

| ISD4003-08MX | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Single-Chip Voice Record/Playback Devices 4-, 5-, 6-, and 8-Minute Durations |

| ISD400308MXD | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Single-Chip Voice Record/Playback Devices 2- to 16-Minute Durations |

发布紧急采购,3分钟左右您将得到回复。