- 您现在的位置:买卖IC网 > PDF目录16601 > ISL6271ACR (Intersil)IC REG PMIC 1BUCK 2LDO 20-QFN PDF资料下载

参数资料

| 型号: | ISL6271ACR |

| 厂商: | Intersil |

| 文件页数: | 13/16页 |

| 文件大小: | 0K |

| 描述: | IC REG PMIC 1BUCK 2LDO 20-QFN |

| 标准包装: | 75 |

| 应用: | 处理器 |

| 电流 - 电源: | 380µA |

| 电源电压: | 2.76 V ~ 5.5 V |

| 工作温度: | -25°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-VFQFN 裸露焊盘 |

| 供应商设备封装: | 20-QFN 裸露焊盘(4x4) |

| 包装: | 管件 |

�� �

�

�

�ISL6271A�

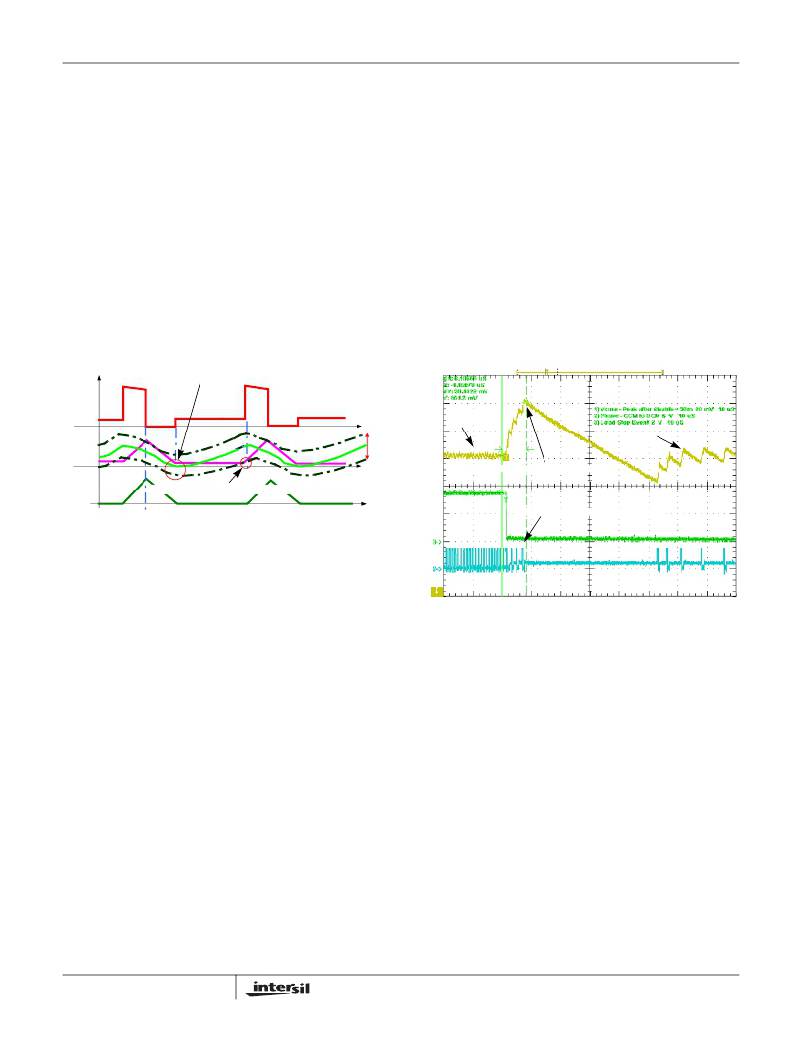

�Light� Load� Operation� -� DCM�

�A� light� load� is� defined� when� the� output� inductor� ripple� current�

�reaches� zero� before� the� next� switching� cycle.� Under� this�

�condition,� the� ISL6271A� synchronous� rectifier� will� turn� off�

�emulating� a� diode� to� prevent� negative� inductor� current.� As�

�explained� below,� the� switching� frequency� and� losses�

�associated� with� turning� on� the� synchronous� rectifier� will� be�

�reduced� to� enhance� the� low� current� efficiency.� The� top�

�waveform� in� Figure� 22� shows� the� phase� voltage� in� DCM.�

�The� middle� waveforms� include� the� error� amplifier� voltage,�

�ripple� capacitor� voltage� and� the� boundaries� of� the� hysteresis�

�comparator� which� track� the� EA� output.� The� waveform� at� the�

�bottom� is� representative� of� the� inductor� current.� Notice� that�

�in� a� switching� cycle� the� inductor� current� rises� as� the� upper�

�P-MOSFET� turns� on,� falls� when� the� lower� N-MOSFET� turns�

�on,� and� stays� at� zero� after� the� current� reaches� zero� as� a�

�result� of� diode� emulation.�

�CLAMPED� VRP>� LOWER� HYS�

�VPH�

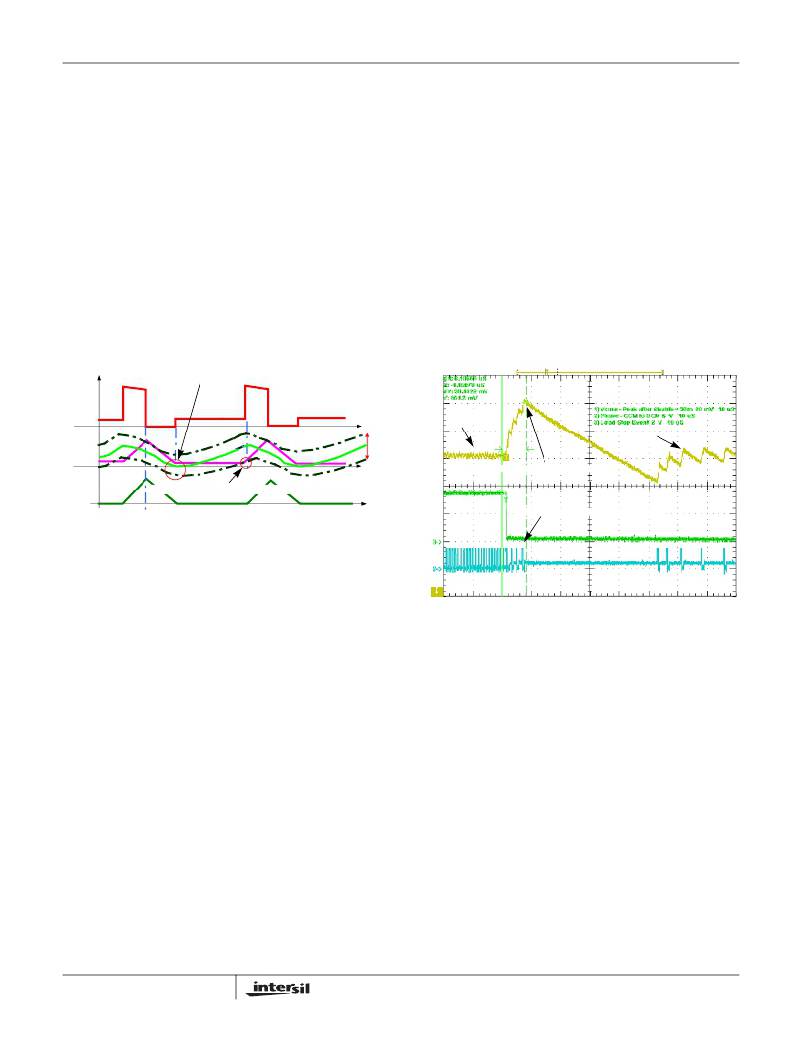

�A� load� transition� from� full� load� to� no� load� will� result� in� a� finite�

�period� of� time� during� which� the� error� amplifier� settles� to� a�

�new� steady� state� condition.� As� illustrated� in� Figure� 23,� the�

�SSR� architecture� inherent� to� the� ISL6271A� responds� within�

�6μs� of� the� mode� change,� slewing� the� error� amplifier� output�

�below� the� clamped� ripple� capacitor� voltage� and� preventing�

�the� upper� FET� from� turning� on.� Prior� to� reaching� the� new�

�stability� point,� the� phase� node� applies� four� phase� pulses�

�before� the� controller� forces� the� output� voltage� to� the�

�prescribed� regulation� point.� Once� the� output� falls� below� the�

�reference� voltage� the� controller� then� pumps� up� the� output�

�voltage� and� enters� its� steady� state� DCM.� Mode� changes� that�

�take� the� converter� from� CCM� into� DCM� will� have� much�

�higher� output� voltage� spike� than� a� load� step� that� remains� in�

�CCM.� Compared� with� competitive� solutions� the� ISL6271A�

�responds� very� well� during� this� severe� mode� change� and� it� is�

�more� than� sufficient� to� meet� Vcore� tolerance� specifications�

�as� required� by� Intel.�

�CCM�

�VCMP�

�VEA�

�VRP�

�LOOP� CLOSES� 6μs� AFTER� MODE� CHANGE�

�DCM�

�CLAMPED VRP = > LOWER HYS�

�ILO�

�PHASE PULSES BEFORE LOOP� IS� CLOSED�

�FIGURE� 22.� SRR� IN� DCM�

�To� understand� the� ISL6271A� light� load� operation,� look�

�carefully� at� the� waveforms� in� the� middle� of� Figure� 22.� Notice�

�that� the� voltage� across� the� ripple� capacitor,� VRP,� has� a�

�minimum� clamp� voltage� (typically� 0.4V),� and� that� the� Error�

�Amplifier� can� go� below� this� voltage� (typically� clamped� to�

�0.2V).� In� DCM,� the� voltage� across� ripple� capacitor� will� be�

�discharged� each� cycle� to� the� clamp� voltage.� While� the� lower�

�hysteresis� is� below� this� voltage,� the� ripple� capacitor� will�

�remain� clamped� keeping� the� upper� P-MOSFET� off.� As� the�

�EA� voltage� increases� so� too� will� the� lower� threshold� of� the�

�hysteresis� window� until� it� reaches� the� ripple� capacitor� clamp�

�voltage� (VCLMP).� At� this� point,� the� upper� FET� will� be�

�enabled� and� will� turn� on.� The� lighter� the� load,� the� lower� the�

�error� amplifier� output� is,� and� the� longer� the� ripple� capacitor�

�voltage� stays� at� the� VCLMP� voltage.� This� results� in� a� phase�

�node� switching� frequency� that� is� proportional� to� load� current�

�(that� is,� lower� switching� losses� and� higher� efficiency� at�

�lighter� loads).� In� DCM� the� switching� frequency� will� be� lower�

�than� in� a� heavy� load,� CCM.�

�13�

�FIGURE� 23.� CCM� TO� DCM� MODE�

�Transition� Between� Light� load� and� Heavy� Load�

�Unlike� most� control� topologies� that� require� two� sets� of�

�circuits� to� control� the� light� and� heavy� load� operation,� the�

�SRR� control� naturally� switches� between� heavy� and� light� load�

�with� the� same� control� circuit.� As� the� load� gets� lighter,� the�

�feedback� forces� the� error� amplifier� output� to� a� lower� voltage�

�and� when� the� lower� threshold� of� the� hysteresis� window� is�

�lower� than� VCLMP,� light� load� operation� begins.� The� scope�

�shot� in� Figure� 24� illustrates� a� mode� transition� from� a� DCM�

�(10mA� load� current)� to� CCM� (170mA)� with� trace� 4� (GRN)�

�being� the� command� pulse� that� initiates� the� mode� change.�

�Prior� to� the� load� step,� and� while� the� converter� is� in� DCM,� the�

�ripple� voltage� is� approximately� 10mV� and� the� ripple�

�frequency� is� 125kHz.� In� CCM,� the� converter� operates� at� a�

�frequency� of� approximately� 10X� that� of� DCM� and� the� ripple�

�is� reduced� by� more� than� a� factor� of� two.�

�FN9171.1�

�相关PDF资料 |

PDF描述 |

|---|---|

| GEM18DRTF | CONN EDGECARD 36POS DIP .156 SLD |

| V150C28E150B2 | CONVERTER MOD DC/DC 28V 150W |

| 1-862545-7 | LEAD ASSY 16AWG SNG END 127MM |

| Q5-3X-1 1/2-01-SS25M | HEATSK DL WL Q53X 1-1/2"X25M BLK |

| VI-B3P-EX | CONVERTER MOD DC/DC 13.8V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6271ACR-T | 功能描述:IC PMIC XSCALE PROCESSOR 20-QFN RoHS:否 类别:集成电路 (IC) >> PMIC - 电源管理 - 专用 系列:- 应用说明:Ultrasound Imaging Systems Application Note 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:37 系列:- 应用:医疗用超声波成像,声纳 电流 - 电源:- 电源电压:2.37 V ~ 6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:56-WFQFN 裸露焊盘 供应商设备封装:56-TQFN-EP(8x8) 包装:管件 |

| ISL6271ACRZ | 功能描述:直流/直流开关调节器 LD PLL & SRAMG FOR I NTEL PROCESSORS IBM RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

| ISL6271ACRZ-T | 功能描述:直流/直流开关调节器 LD PLL & SRAMG FOR I NTEL PROCESSORS IBM RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

| ISL6271AEVAL1 | 功能描述:EVALUATION BOARD FOR ISL6271A RoHS:否 类别:编程器,开发系统 >> 评估板 - DC/DC 与 AC/DC(离线)SMPS 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:True Shutdown™ 主要目的:DC/DC,步升 输出及类型:1,非隔离 功率 - 输出:- 输出电压:- 电流 - 输出:1A 输入电压:2.5 V ~ 5.5 V 稳压器拓扑结构:升压 频率 - 开关:3MHz 板类型:完全填充 已供物品:板 已用 IC / 零件:MAX8969 |

| ISL6271CR | 制造商:Rochester Electronics LLC 功能描述:PLL & SRAM REGULATOR FOR INTEL PROCESSORS - Bulk 制造商:Intersil Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。