参数资料

| 型号: | ISL6329IRZ-T |

| 厂商: | Intersil |

| 文件页数: | 6/38页 |

| 文件大小: | 0K |

| 描述: | IC CTRLR PWM SYNC BUCK DL 60QFN |

| 标准包装: | 4,000 |

| 应用: | 控制器,AMD SVI |

| 输入电压: | 5 V ~ 12 V |

| 输出数: | 2 |

| 输出电压: | 0.0125 V ~ 1.55 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | * |

| 封装/外壳: | * |

| 供应商设备封装: | * |

| 包装: | * |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

�� �

�

�

�ISL6329�

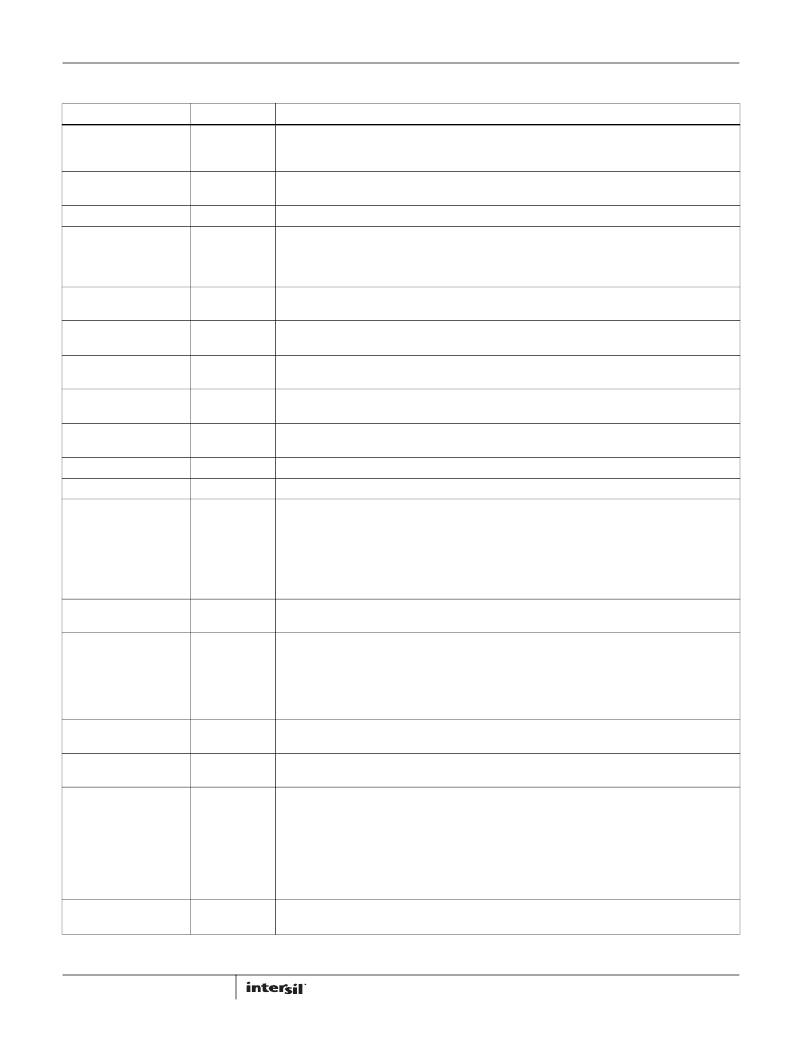

�Functional� Pin� Descriptions� (Continued)�

�PIN� NAME�

�SDA�

�VCC�

�RSVD�

�OFS�

�OCP�

�TCOMP1,� TCOMP2�

�RGND�

�VSEN�

�FB_PSI�

�FB�

�COMP�

�FS�

�PIN� NUMBER�

�9�

�10�

�11�

�12�

�13�

�14,� 15�

�16�

�17�

�18�

�19�

�20�

�21�

�DESCRIPTION�

�Connect� this� pin� to� the� bidirectional� data� line� of� the� I� 2� C� bus,� which� is� a� logic� level� input/output� signal.�

�All� I� 2� C� data� is� sent� over� this� line,� including� the� address� of� the� device� the� bus� is� trying� to� communicate�

�with� and� what� functions� the� device� should� perform.�

�VCC� is� the� bias� supply� for� the� ICs� small-signal� circuitry.� Connect� this� pin� to� a� +5V� supply� and� decouple�

�using� a� quality� 0.1μF� ceramic� capacitor.�

�RESERVED.� Connect� this� pin� directly� to� the� VCC� pin.�

�The� OFS� pin� provides� a� means� to� program� a� DC� current� for� generating� an� offset� voltage� across� the� resistor�

�between� FB� and� VSEN.� The� offset� current� is� generated� via� an� external� resistor� and� precision� internal�

�voltage� references.� The� polarity� of� the� offset� is� selected� by� connecting� the� resistor� to� GND� or� VCC.� For� no�

�offset,� the� OFS� pin� should� be� left� unconnected.�

�A� capacitor� from� this� pin� to� ground� determines� the� time� that� the� regulator� is� allowed� to� service� a� load�

�current� spike� that� exceeds� the� internal� OCP� trip� point.�

�These� two� pins� are� used� to� compensate� the� inductor� current� sensing� for� fluctuations� due� to�

�temperature.�

�Inverting� input� to� the� Core� and� Northbridge� regulator� precision� differential� remote-sense� amplifiers.� This�

�pin� should� be� connected� to� the� remote� ground� sense� pin� of� the� processor� core,� VSS_SENSE.�

�Non-inverting� input� to� the� Core� regulator� precision� differential� remote-sense� amplifier.� This� pin� should� be�

�connected� to� the� remote� Core� sense� pin� of� the� processor,� VDD_SENSE.�

�In� PSI� mode� this� pin� is� internally� shorted� to� the� FB� pin� to� augment� the� feedback� compensation� network�

�for� the� lower� phase� count.�

�Inverting� input� to� the� internal� error� amplifier� for� the� Core� regulator.�

�Output� of� the� internal� error� amplifier� for� the� Core� regulator.�

�This� is� a� dual� function� pin.� A� resistor,� placed� from� FS� to� either� Ground� or� VCC� sets� the� switching�

�frequency� of� both� controllers.� Refer� to� Equation� 1� for� proper� resistor� calculation.�

�R� T� =� 10�

�[� 10.61� –� 1.035� log� (� f� s� )� ]�

�(EQ.� 1)�

�If� the� resistor� is� tied� to� ground,� the� number� of� active� phases� in� PSI� mode� is� 1.� If� the� resistor� is� tied� to�

�VCC,� the� number� of� active� phases� in� PSI� mode� is� 2.�

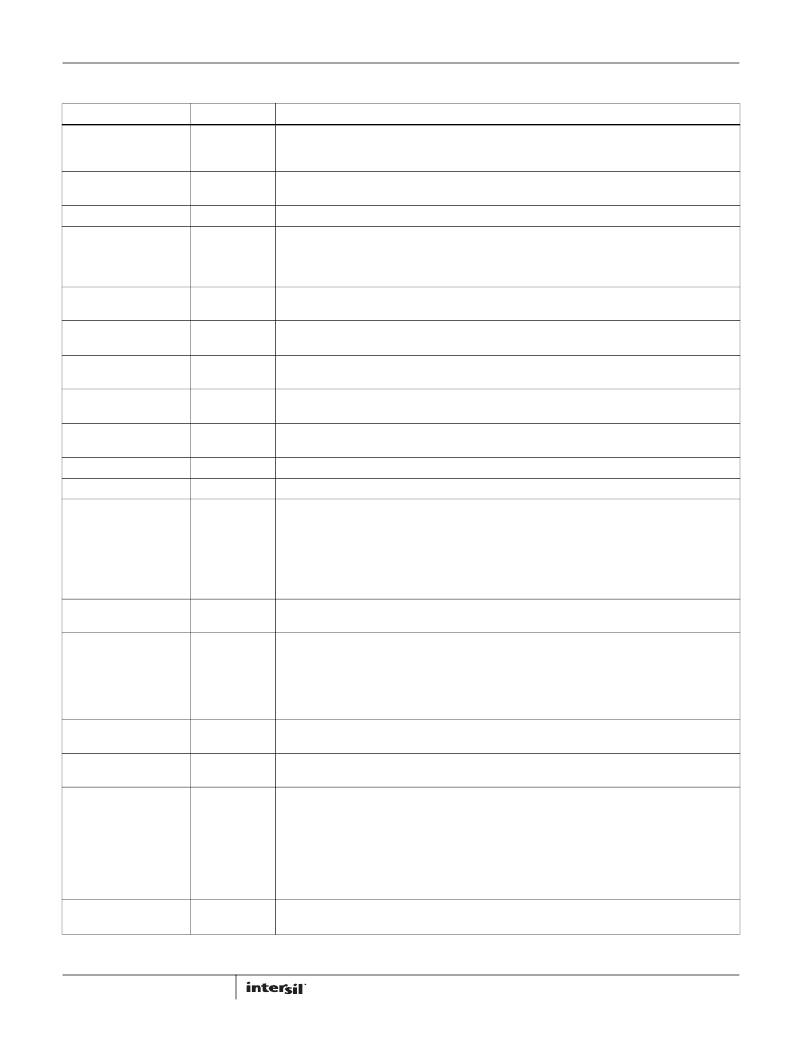

�APA�

�ISENn+,� ISENn-,�

�ISEN_NB+,� ISEN_NB-�

�PHASE1,� PHASE2�

�GND�

�EN�

�UGATE1,� UGATE2�

�22�

�23,� 24,� 25,� 26,�

�27,� 28,� 53,� 54,�

�55,� 56,� 57,� 58,�

�59,� 60�

�40,� 29�

�30,� 32,� 61�

�31�

�39,� 33�

�6�

�Allows� for� programming� of� the� Auto� Phase� Alignment� threshold.� A� resistor� in� parallel� with� a� capacitor�

�to� ground� is� used� to� set� this� threshold.�

�These� pins� are� used� for� differentially� sensing� the� corresponding� channel� output� currents.� The� sensed�

�currents� are� used� for� channel� balancing,� protection,� and� core� load� line� regulation.�

�Connect� ISEN-� to� the� node� between� the� RC� sense� elements� surrounding� the� inductor� of� the� respective�

�channel.� Tie� the� ISEN+� pin� to� the� other� end� of� the� sense� capacitor� through� a� resistor,� R� ISEN� .� The� voltage�

�across� the� sense� capacitor� is� proportional� to� the� inductor� current.� The� sense� current,� therefore,� is�

�proportional� to� the� inductor� current� and� scaled� by� the� DCR� of� the� inductor� and� R� ISEN� .�

�Connect� these� pins� to� the� sources� of� the� corresponding� upper� MOSFETs.� These� pins� are� the� return� path�

�for� the� upper� MOSFET� drives.�

�Bias� and� reference� ground� for� the� IC.� The� GND� connection� for� the� ISL6329� is� made� with� three� pins� and�

�through� the� thermal� pad� on� the� bottom� of� the� package.�

�This� pin� is� a� threshold-sensitive� (approximately� 0.85V)� system� enable� input� for� the� controller.� Held� low,� this�

�pin� disables� both� CORE� and� NB� controller� operation.� Pulled� high,� the� pin� enables� both� controllers� for�

�operation.�

�A� second� function� of� this� pin� is� to� provide� driver� bias� monitor� for� external� drivers.� A� resistor� divider� with� the�

�center� tap� connected� to� this� pin� from� the� drive� bias� supply� prevents� enabling� the� controller� before�

�insufficient� bias� is� provided� to� external� driver.� The� resistors� should� be� selected� such� that� when� the� POR-�

�trip� point� of� the� external� driver� is� reached,� the� voltage� at� this� pin� meets� the� above� mentioned� threshold�

�level.�

�Connect� this� pin� to� the� corresponding� upper� MOSFET� gate.� This� pin� provides� the� PWM-controlled� gate�

�drive� for� the� upper� MOSFET� and� is� monitored� for� shoot-through� prevention� purposes.�

�FN7800.0�

�April� 19,� 2011�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6333IRZ | IC CTRLR PWM 3PHASE BUCK 48-QFN |

| ISL6334AIRZR5368 | IC CTRLR PWM 4PHASE BUCK 40QFN |

| ISL6334BIRZ-T | IC CTRLR PWM SYNC BUCK 40-QFN |

| ISL6334CRZ | IC CTRLR PWM 4PHASE BUCK 40-QFN |

| ISL6334DIRZ | IC CTRLR PWM 4PHASE VR11.1 40QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6333ACRZ | 功能描述:IC CTRLR PWM 3PHASE BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6333ACRZ-T | 功能描述:IC CTRLR PWM 3PHASE BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6333AEVAL1Z | 制造商:Intersil Corporation 功能描述: |

| ISL6333AIRZ | 功能描述:IC CTRLR PWM 3PHASE BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:2,000 系列:- 应用:控制器,DSP 输入电压:4.5 V ~ 25 V 输出数:2 输出电压:最低可调至 1.2V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:30-TFSOP(0.173",4.40mm 宽) 供应商设备封装:30-TSSOP 包装:带卷 (TR) |

| ISL6333AIRZ-T | 功能描述:IC CTRLR PWM 3PHASE BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。