参数资料

| 型号: | ISL6336AIRZ |

| 厂商: | Intersil |

| 文件页数: | 20/31页 |

| 文件大小: | 0K |

| 描述: | IC CTRLR PWM 6PHASE BUCK 48-QFN |

| 标准包装: | 43 |

| 应用: | 控制器,Intel VR11.1 |

| 输入电压: | 3 V ~ 12 V |

| 输出数: | 1 |

| 输出电压: | 0.5 V ~ 1.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘 |

| 供应商设备封装: | 48-QFN(7x7) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页

�� �

�

�

�ISL6336,� ISL6336A�

�V� IMON� =� -------------------� ?� ------------------� ?� I� OUT�

�R� ISEN�

�soft-start� ramp� until� the� voltage� reaches� the� VID� voltage�

�minus� the� offset� voltage.�

�N�

�R� IMON� R� X�

�(EQ.� 17)�

�where� V� IMON� is� the� voltage� at� the� IMON� pin,� R� IMON� is� the�

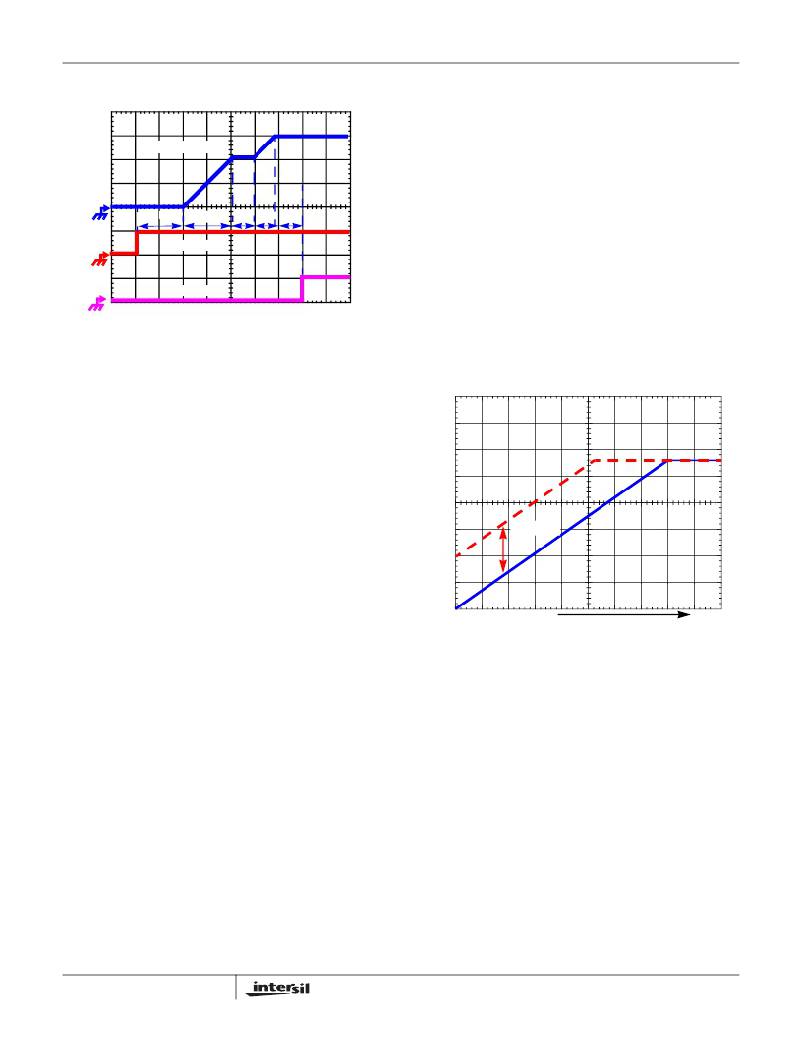

�V� OUT� ,� 500mV/DIV�

�resistor� between� IMON� and� GND,� I� OUT� is� the� total� output�

�current� of� the� converter,� R� ISEN� is� the� sense� resistor�

�connected� to� the� ISEN+� pin,� N� is� the� active� channel� number�

�and� R� X� is� the� DC� resistance� of� the� current� sense� element.�

�t� D1�

�t� D2�

�t� D3� t� D4�

�t� D5�

�The� resistor� from� the� IMON� pin� to� GND� should� be� chosen� to�

�ensure� that� the� voltage� at� the� IMON� pin� is� less� than� 1.12V�

�t� SS� =� t� D1� +� t� D2� +� t� D3� +� t� D4�

�EN_VTT�

�VR_RDY�

�500μs/DIV�

�FIGURE� 9.� SOFT-START� WAVEFORMS�

�The� soft-start� time� is� the� sum� of� the� 4� periods� as� shown� in�

�Equation� 14:�

�(EQ.� 14)�

�t� D1� is� a� fixed� delay� with� a� typical� value� as� 1.36ms.� t� D3� is�

�determined� by� a� fixed� 85μs� plus� the� time� to� obtain� valid� VID�

�voltage.� If� the� VID� is� valid� before� the� output� reaches� the�

�1.1V,� the� minimum� time� to� validate� the� VID� input� is� 500ns.�

�Therefore� the� minimum� t� D3� is� about� 86μs.�

�During� t� D2� and� t� D4� ,� ISL6336,� ISL6336A� digitally� controls� the�

�DAC� voltage� change� at� 6.25mV� per� step.� The� time� for� each�

�step� is� determined� by� the� frequency� of� the� soft-start� oscillator,�

�which� is� defined� by� a� resistor� R� SS� from� SS� pin� to� GND� or�

�VCC.� The� equations� are� the� same� for� the� case� where� R� SS� is�

�connected� to� GND� or� VCC.� The� two� soft-start� ramp� times� t� D2�

�under� the� maximum� load� current.� The� IMON� pin� voltage� is�

�clamped� at� a� maximum� of� 1.12V.� Once� the� 1.12V� threshold�

�is� reached,� an� overcurrent� shutdown� will� be� initiated� as�

��A� small� capacitor� can� be� placed� between� the� IMON� pin� and�

�GND� to� reduce� noise.� In� addition,� some� applications� will�

�require� the� V� IMON� signal� to� be� filtered� with� a� minimum� time�

�constant.� The� filter� capacitor� can� be� chosen� appropriately�

�based� on� the� R� IMON� value� to� set� the� desired� time� constant.�

�V� IMON_OFS�

�t� D2� =� ------------------------� (� μ� s� )�

�6.25� ?� 25�

�and� t� D4� can� be� calculated� based� on� the� Equations� 15� and� 16:�

�1.1� ?� R� SS�

�(EQ.� 15)�

�0V�

�0A� LOAD� INCREASING�

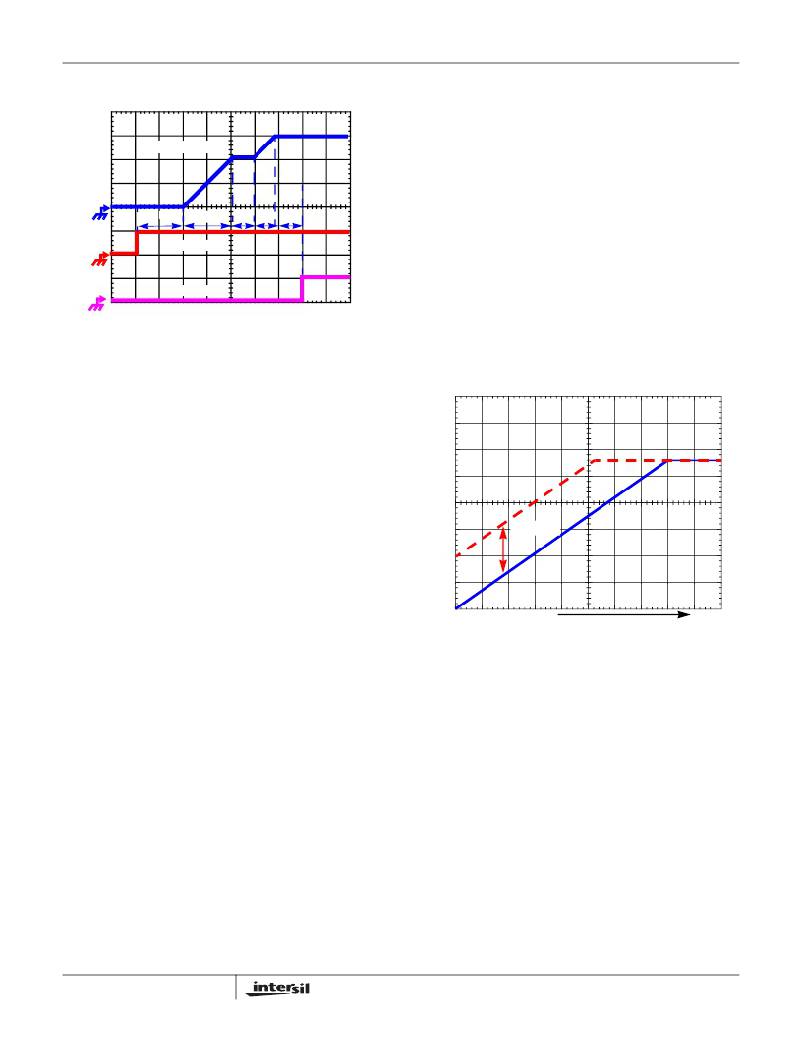

�FIGURE� 10.� IMON� VOLTAGE� vs� OUTPUT� CURRENT�

�t� D4� =� ------------------------------------------------------� (� μ� s� )�

�(� (� V� VID� –� 1.1� )� ?� R� SS� )�

�6.25� ?� 25�

�(EQ.� 16)�

�The� voltage� at� the� IMON� pin� will� vary� linearly� with� output�

�current,� as� shown� in� Figure� 10� with� some� tolerance.� Some�

�applications� may� require� the� addition� of� a� positive� offset� on�

�For� example,� when� VID� is� set� to� 1.5V� and� the� R� SS� is� set� at�

�100k� Ω� ,� the� first� soft-start� ramp� time� t� D2� will� be� 704μs� and� the�

�second� soft-start� ramp� time� t� D4� will� be� 256μs.�

�After� the� DAC� voltage� reaches� the� final� VID� setting,�

�VR_RDY� will� be� set� to� high� with� the� fixed� delay� t� D5� .� The�

�IMON� to� offset� for� the� tolerance� at� the� maximum� IMON�

�voltage� value.� This� can� be� done� by� connecting� a� resistor�

�from� the� IMON� pin� to� VCC� as� shown� in� Figure� 11.� The�

�required� value� for� R� VCC� can� be� determined� by� using�

�Equation� 18:�

�R� VCC� =� ---------------------------------------------------------------------------------------------------------------------�

�typical� value� for� t� D5� is� 85μs.� Before� VR_RDY� is� released,�

�the� controller� disregards� the� PSI#� input� and� always� operates�

�in� normal� CCM� PWM� mode.�

�R� IMON� ?� (� VCC� –� V� IMONOFS� –� V� IMONMAX� )�

�V� IMONOFS�

�(EQ.� 18)�

�Current� Sense� Output�

�The� current� sourced� at� the� IMON� pin� is� equal� to� the� sensed�

�average� current� inside� the� ISL6336,� ISL6336A,� I� AVG� .� In� a�

�typical� application,� a� resistor� is� placed� from� the� IMON� pin� to�

�GND� to� generate� a� voltage� which� is� proportional� to� the� load�

�current� as� shown� in� Equation� 17�

�20�

�where� R� IMON� is� the� resistor� from� IMON� to� GND,� V� IMONOFS�

�is� the� desired� offset� voltage� at� V� IMONMAX� ,� and� V� IMONMAX�

�is� the� voltage� at� IMON� at� the� maximum� load� current.�

�For� example,� if� the� maximum� IMON� voltage� is� 900mV� at� full�

�load� and� the� required� offset� voltage� is� 50mV� and� R� IMON� is�

�10k� Ω� then� R� VCC� should� be� 810k� Ω� .� R� IMON� should� be�

�connected� to� GND� near� the� load� to� increase� accuracy.�

�FN6504.1�

�May� 28,� 2009�

�相关PDF资料 |

PDF描述 |

|---|---|

| X40030S14I-B | IC VOLTAGE MONITOR TRPL 14-SOIC |

| ISL6336CRZ | IC CTRLR PWM 6PHASE BUCK 48-QFN |

| X40030S14I-AT1 | IC VOLTAGE MONITOR TRPL 14-SOIC |

| ASC25DREH-S13 | CONN EDGECARD 50POS .100 EXTEND |

| ASM11DSAN | CONN EDGECARD 22POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6336AIRZ-T | 功能描述:IC CTRLR PWM 6PHASE BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6336BCRZ | 功能描述:IC CTRLR PWM SYNC BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,000 系列:- 应用:电源,ICERA E400,E450 输入电压:4.1 V ~ 5.5 V 输出数:10 输出电压:可编程 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:42-WFBGA,WLCSP 供应商设备封装:42-WLP 包装:带卷 (TR) |

| ISL6336BCRZ-T | 功能描述:IC CTRLR PWM SYNC BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6336BIRZ | 功能描述:IC CTRLR PWM SYNC BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,000 系列:- 应用:电源,ICERA E400,E450 输入电压:4.1 V ~ 5.5 V 输出数:10 输出电压:可编程 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:42-WFBGA,WLCSP 供应商设备封装:42-WLP 包装:带卷 (TR) |

| ISL6336BIRZ-T | 功能描述:IC CTRLR PWM SYNC BUCK 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。