参数资料

| 型号: | ISL6557ACB-T |

| 厂商: | Intersil |

| 文件页数: | 10/18页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM VM 24-SOIC |

| 标准包装: | 1,000 |

| PWM 型: | 电压模式 |

| 输出数: | 1 |

| 频率 - 最大: | 250kHz |

| 占空比: | 75% |

| 电源电压: | 4.75 V ~ 5.25 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 24-SOIC(0.295",7.50mm 宽) |

| 包装: | 带卷 (TR) |

�� �

�

�

�ISL6557A�

�OVERVOLTAGE� PROTECTION�

�The� ISL6557A� detects� output� voltages� above� 2.1V� and�

�is� below� the� POR-rising� threshold,� the� PWM� outputs� are� held�

�in� a� high-impedance� state� to� assure� the� drivers� remain� off.�

�immediately� commands� all� PWM� outputs� low.� This� directs�

�the� Intersil� drivers� turn� on� the� lower� MOSFETs� and� protect�

�the� load� by� preventing� any� further� increase� in� output� voltage.�

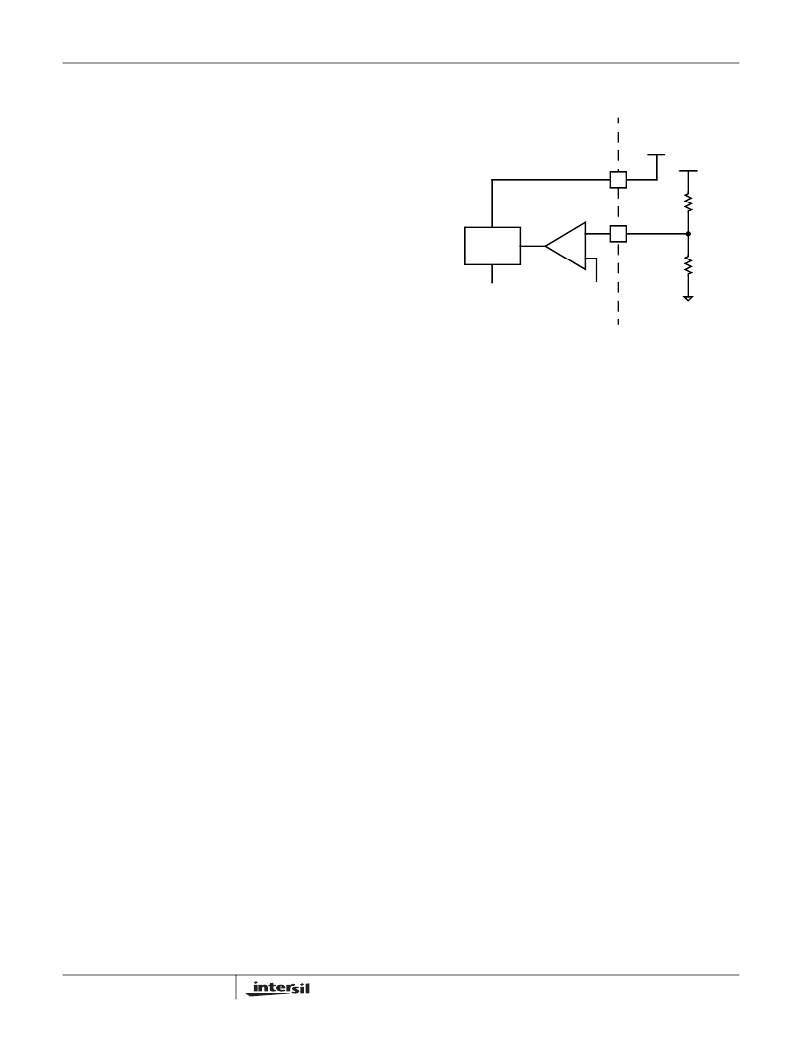

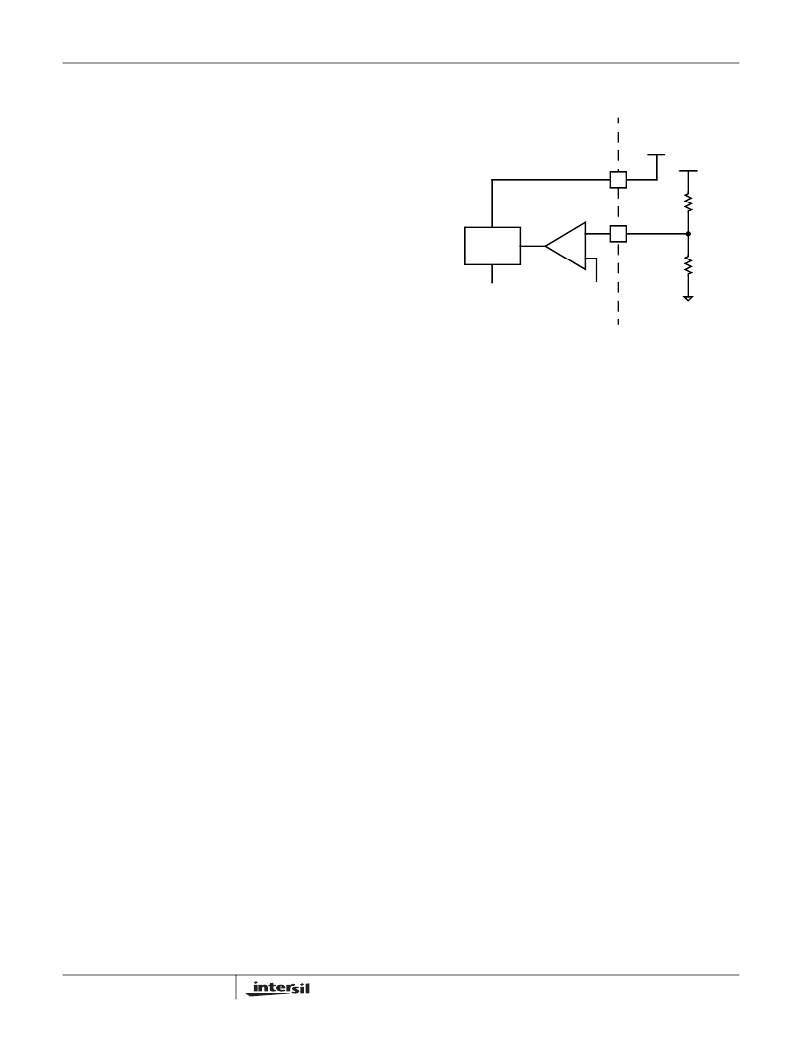

�ISL6557A� INTERNAL� CIRCUIT�

�EXTERNAL� CIRCUIT�

�+� 5V�

�Once� the� output� voltage� falls� to� the� level� set� by� the� VID�

�code,� the� PWM� outputs� enter� high-impedance� mode.� The�

�Intersil� drivers� respond� by� turning� off� both� upper� and� lower�

�MOSFETs.� If� the� overvoltage� condition� reoccurs,� the�

�ENABLE�

�COMPARATOR�

�VCC�

�+� 12� V�

�10.7k� Ω�

�ISL6557A� will� again� command� the� lower� MOSFETs� to� turn�

�on.� The� ISL6557A� will� continue� to� protect� the� load� in� this�

�fashion� as� long� as� the� overvoltage� repeats.�

�After� detecting� an� overvoltage� condition,� the� ISL6557A�

�ceases� normal� PWM� operation� until� it� is� reset� by� power� cycle�

�POR�

�CIRCUIT�

�OV� LATCH�

�SIGNAL�

�+�

�-�

�1.23V� (±� 2%)�

�EN�

�1.40k� Ω�

�in� which� VCC� is� removed� below� the� POR� falling� threshold�

�and� restored� above� the� POR� rising� threshold� as� described� in�

�Enable� and� Disable� and� Electrical� Specifications� .�

�LOAD-LINE� REGULATION�

�In� applications� with� high� transient� current� slew� rates,� the�

�lowest-cost� solution� for� maintaining� regulation� often� requires�

�some� kind� of� controlled� output� impedance.� Pin� 8� of� the�

�ISL6557A� carries� a� current� proportional� to� the� average�

�current� of� all� active� channels.� The� current� is� equivalent� to�

�I� AVG� in� Figures� 5� and� 7.� Connecting� FB� and� IOUT� together�

�forces� I� AVG� into� the� summing� node� of� the� error� amplifier� and�

�produces� a� voltage� drop� across� the� feedback� resistor,� R� FB� ,�

�proportional� to� the� output� current.� In� Figure� 7,� the� steady-�

�state� value� of� V� DROOP� is� simply�

�FIGURE� 8.� START-UP� CONDITION� USING� THRESHOLD-�

�SENSITIVE� ENABLE� (EN)� FUNCTION�

�After� power� on,� the� ISL6557A� remains� in� shut-down� mode�

�until� the� voltage� at� the� enable� input� (EN)� rises� above� 1.23V�

�(±2%).� This� optional� feature� prevents� the� ISL6557A� from�

�operating� until� the� connected� voltage� rail� is� available� and�

�above� some� selectable� threshold.� For� example,� the�

�HIP660X� family� of� MOSFET� driver� ICs� require� 12V� bias,� and�

�in� certain� circumstances,� it� can� be� important� to� assure� that�

�the� drivers� reach� their� POR� level� before� the� ISL6557A�

�becomes� enabled.� The� schematic� in� Figure� 8� demonstrates�

�coordination� of� the� ISL6557A� with� HIP660X� family� of�

�MOSFET� driver� ICs.� The� enable� comparator� has� about�

�V� DROOP� =� I� AVG� R� FB�

�(EQ.� 3)�

�70mV� of� hysteresis� to� prevent� bounce.� To� defeat� the�

�threshold-sensitive� enable,� connect� EN� to� VCC.�

�I� AVG� =� -------------�

�N�

�R� ISEN�

�V� DROOP� =� -------------� ----------------------� R� FB�

�In� the� case� that� each� channel� uses� the� same� value� for� RISEN� to�

�sense� channel� current,� and� this� is� almost� always� true,� a� more�

�complete� expression� for� VDROOP� can� be� determined� from� the�

�expression� for� IAVG� as� it� is� derived� from� Figures� 4� and� 5.�

�I� OUT� r� DS� (� ON� )�

�----------------------�

�(EQ.� 4)�

�I� OUT� r� DS� (� ON� )�

�R� ISEN�

�ENABLE� AND� DISABLE�

�The� internal� power-on� reset� circuit� (POR)� prevents� the�

�ISL6557A� from� starting� before� the� bias� voltage� at� VCC�

�reaches� the� POR-rising� threshold� as� defined� in� Electrical�

�Specifications� .The� POR� level� is� high� enough� to� guarantee�

�that� all� parts� of� the� ISL6557A� can� perform� their� functions�

�The� 11111� VID� code� is� reserved� as� a� signal� to� the� controller�

�that� no� load� is� present.� The� controller� will� enter� shut-down�

�mode� after� receiving� this� code� and� will� start� up� upon�

�receiving� any� other� code.�

�To� enable� the� controller,� VCC� must� be� greater� than� the� POR�

�threshold;� the� voltage� on� EN� must� be� greater� than� 1.23V� and�

�VID� cannot� be� equal� to� 11111.� Once� these� conditions� are�

�true,� the� controller� immediately� initiates� a� soft� start�

�sequence.�

�SOFT-START�

�The� soft-start� time,� t� SS� ,� is� determined� by� an� 11-bit� counter�

�that� increments� with� every� pulse� of� the� phase� clock.� For�

�example,� a� converter� switching� at� 250kHz� has� a� soft-start�

�time� of�

�T� SS� =� -------------� =� 8.2ms�

�properly.� Built-in� hysteresis� assures� that� once� enabled,� the�

�ISL6557A� will� not� turn� off� unless� the� bias� voltage� falls� to�

�approximately� 0.5V� below� the� POR-rising� level.� When� VCC�

�10�

�2048�

�f� SW�

�(EQ.� 5)�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6558IR-T | IC REG CTRLR BUCK PWM 20-QFN |

| ISL6559CBZ-T | IC REG CTRLR BUCK PWM VM 28-SOIC |

| ISL6561CR-T | IC CTRLR PWM MULTIPHASE 40-QFN |

| ISL6563IR-T | IC CTRLR PWM MULTIPHASE 24-QFN |

| ISL6564AIRZ | IC REG CTRLR BUCK PWM VM 40-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6557ACBZ | 功能描述:IC REG CTRLR BUCK PWM VM 24-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6557ACBZ-T | 功能描述:IC REG CTRLR BUCK PWM VM 24-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6557CB | 制造商:Intersil Corporation 功能描述: |

| ISL6557CB-T | 制造商:Intersil Corporation 功能描述: |

| ISL6557CB-T WAF | 制造商:Intersil Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。