- 您现在的位置:买卖IC网 > PDF目录11595 > KSZ8873MLL (Micrel Inc)IC ETHERNET SWITCH 3PORT 64-LQFP PDF资料下载

参数资料

| 型号: | KSZ8873MLL |

| 厂商: | Micrel Inc |

| 文件页数: | 42/115页 |

| 文件大小: | 0K |

| 描述: | IC ETHERNET SWITCH 3PORT 64-LQFP |

| 产品培训模块: | KSZ8873 Ethernet Switches |

| 特色产品: | KSZ8873 Ethernet Switch Controller |

| 标准包装: | 160 |

| 控制器类型: | 以太网开关控制器 |

| 接口: | MII |

| 电源电压: | 1.8V,2.5V,3.3V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 托盘 |

| 产品目录页面: | 1081 (CN2011-ZH PDF) |

| 其它名称: | 576-3459 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页

Micrel, Inc.

KSZ8873MLL/FLL/RLL

September 20, 2013

32

Revision 1.6

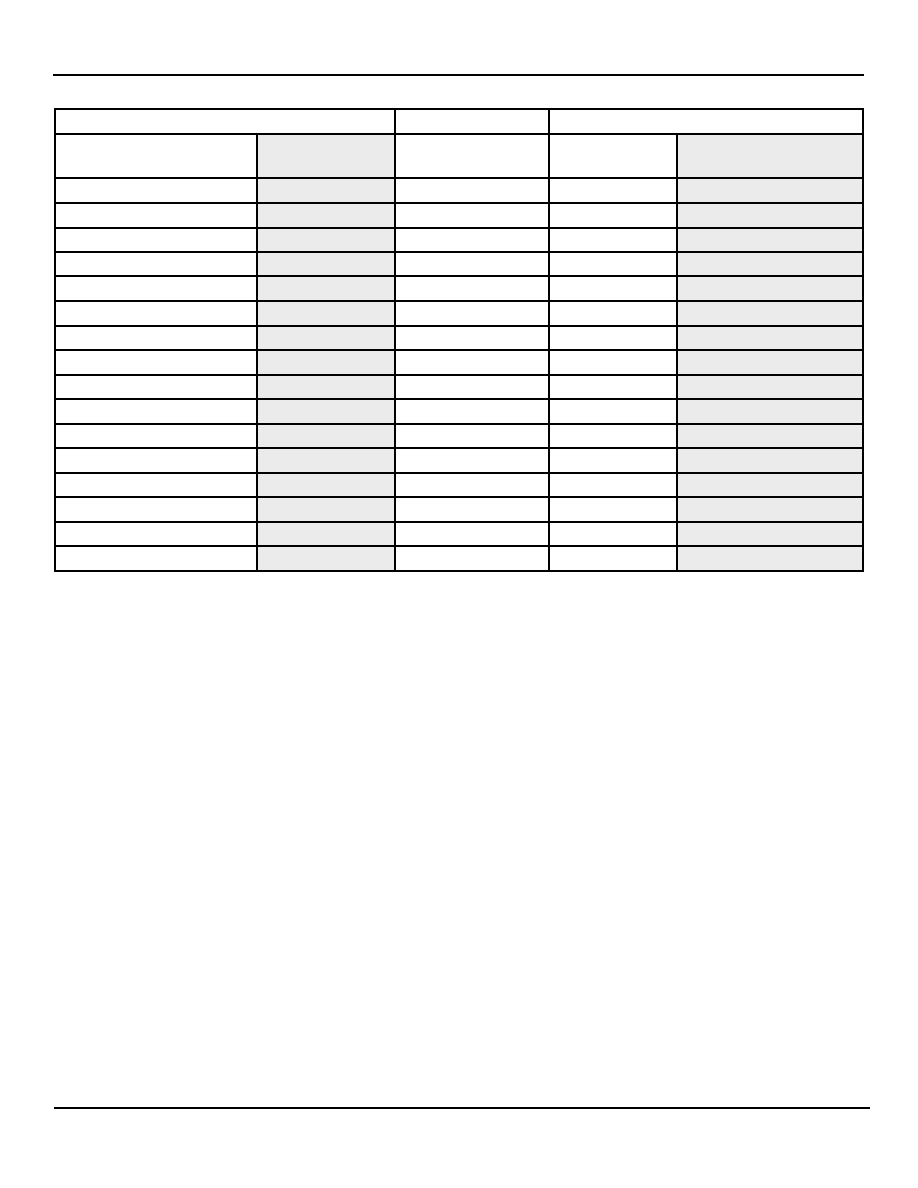

Table 4. MII Signals

PHY-Mode Connections

MAC-Mode Connections

External MAC

Controller Signals

KSZ8873MLL/FL

PHY Signals

Pin Descriptions

External

PHY Signals

KSZ8873MLL/FLL

MAC Signals

MTXEN

SMTXEN3

Transmit enable

MTXEN

SMRXDV3

MTXER

SMTXER3

Transmit error

MTXER

(not used)

MTXD3

SMTXD33

Transmit data bit 3

MTXD3

SMRXD33

MTXD2

SMTXD32

Transmit data bit 2

MTXD2

SMRXD32

MTXD1

SMTXD31

Transmit data bit 1

MTXD1

SMRXD31

MTXD0

SMTXD30

Transmit data bit 0

MTXD0

SMRXD30

MTXC

SMTXC3

Transmit clock

MTXC

SMRXC3

MCOL

SCOL3

Collision detection

MCOL

SCOL3

MCRS

SCRS3

Carrier sense

MCRS

SCRS3

MRXDV

SMRXDV3

Receive data valid

MRXDV

SMTXEN3

MRXER

(not used)

Receive error

MRXER

SMTXER3

MRXD3

SMRXD33

Receive data bit 3

MRXD3

SMTXD33

MRXD2

SMRXD32

Receive data bit 2

MRXD2

SMTXD32

MRXD1

SMRXD31

Receive data bit 1

MRXD1

SMTXD31

MRXD0

SMRXD30

Receive data bit 0

MRXD0

SMTXD30

MRXC

SMRXC3

Receive clock

MRXC

SMTXC3

The MII operates in either PHY mode or MAC mode. The data interface is a nibble wide and runs at the network bit rate

(not encoded). Additional signals on the transmit side indicate when data is valid or when an error occurs during

transmission. Similarly, the receive side has signals that convey when the data is valid and without physical layer errors.

For half duplex operation, the SCOL signal indicates if a collision has occurred during transmission.

The KSZ8873MLL/FLL does not provide the MRXER signal for PHY mode operation and the MTXER signal for MAC

mode operation. Normally, MRXER indicates a receive error coming from the physical layer device and MTXER indicates

a transmit error from the MAC device. Since the switch filters error frames, these MII error signals are not used by the

KSZ8873MLL/FLL. So, for PHY mode operation, if the device interfacing with the KSZ8873MLL/FLL has an MRXER input

pin, it needs to be tied low. And, for MAC mode operation, if the device interfacing with the KSZ8873MLL/FLL has an

MTXER input pin, it also needs to be tied low.

The KSZ8873MLL/FLL provides a bypass feature in the MII PHY mode. Pin SMTXER3/MII_LINK is used for MII link

status. If the host is power down, Pin MII_LINK will go to high. In this case, no new ingress frames from port1 or port 2 will

be sent out through port 3, and the frames for port 3 already in packet memory will be flushed out.

RMII Interface Operation

The Reduced Media Independent Interface (RMII) specifies a low pin count Media Independent Interface (MII). RMII

provides a common interface between physical layer and MAC layer devices, and has the following key characteristics:

1.

Ports 10Mbps and 100Mbps data rates.

2.

Uses a single 50 MHz clock reference (provided internally or externally).

3.

Provides independent 2-bit wide (di-bit) transmit and receive data paths.

4.

Contains two distinct groups of signals: one for transmission and the other for reception

When EN_REFCLKO_3 is high, KSZ8873RLL will output a 50MHz in REFCLKO_3. Register 198 bit[3] is used to select

internal or external reference clock. Internal reference clock means that the clock for the RMII of KSZ8873RLL will be

相关PDF资料 |

PDF描述 |

|---|---|

| KSZ8863RLL | IC ETHERNET SW 3PORT 48-LQFP |

| KSZ8863MLL | IC ETHERNET SW 3PORT 48-LQFP |

| KSZ8863FLL | IC ETHERNET SW 3PORT 48-LQFP |

| LTC4267IDHC#PBF | IC POE 802.3AF INTERFACE 16-DFN |

| 000-68175-11RFX | BNC PLUG CRIMP PLENUM 59 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8873MLL AM | 功能描述:以太网 IC 3-Port 10/100 Ethernet Switch with 1x MII Interface (Automotive Grade, Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8873MLL AM TR | 功能描述:以太网 IC 3-Port 10/100 Ethernet Switch with 1x MII Interface (Automotive Grade, Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8873MLL/8863MLL | 制造商:Micrel Inc 功能描述:EVAL BOARD |

| KSZ8873MLL_09 | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:Integrated 3-Port 10/100 Managed Switch with PHYs |

| KSZ8873MLL_11 | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:Integrated 3-Port 10/100 Managed Switch with PHYs |

发布紧急采购,3分钟左右您将得到回复。