- 您现在的位置:买卖IC网 > PDF目录369885 > LXT384BE Telecomm/Datacomm PDF资料下载

参数资料

| 型号: | LXT384BE |

| 元件分类: | 通信、网络模块及开发工具 |

| 英文描述: | Telecomm/Datacomm |

| 中文描述: | 电信/数据通信 |

| 文件页数: | 42/80页 |

| 文件大小: | 1112K |

| 代理商: | LXT384BE |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

LXT384

—

Octal T1/E1/J1 Transceiver

42

Datasheet

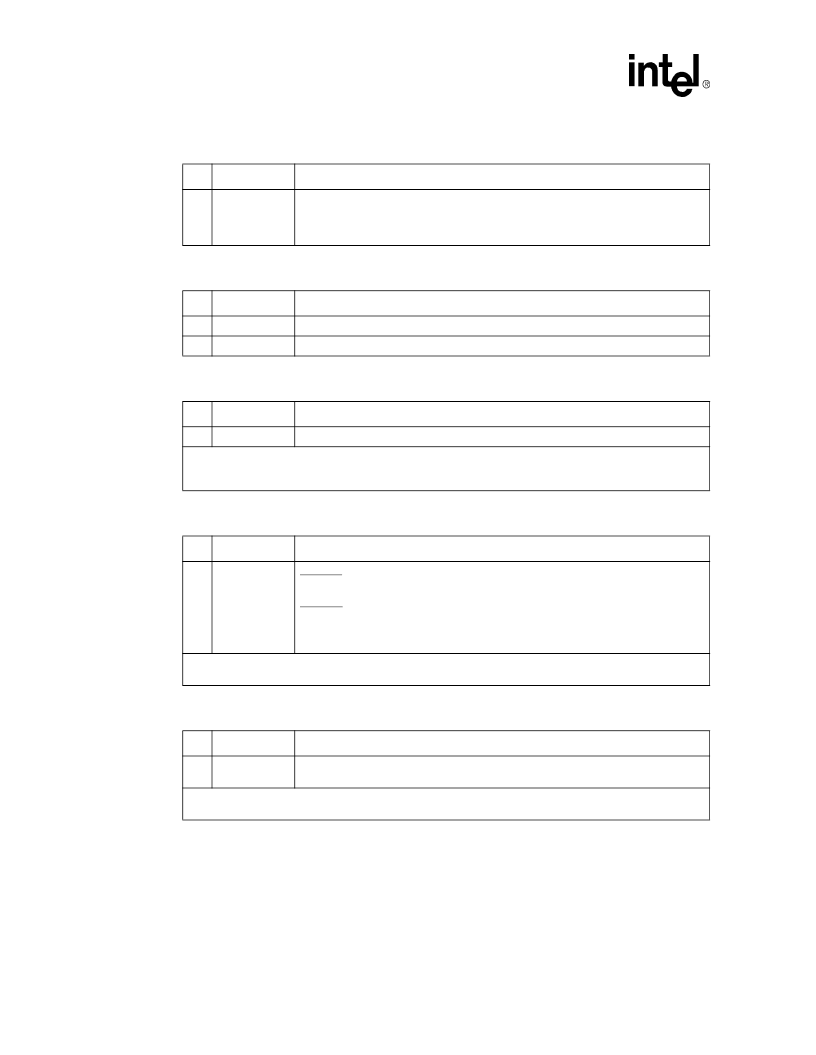

Table 18. Software Reset Register, RES (0Ah)

Bit

Name

Function

7-0

RES7-RES0

Writing to this register initiates a 1 microsecond reset cycle, except in Intel non-

multiplexed mode. This operation sets all LXT384 registers to their default values.

When using Intel non-multiplexed host mode, extend cycle time to 2 microseconds.

Please refer to Host Mode section for details.

Table 19. Performance Monitoring Register, MON (0Bh)

Bit

Name

Function

3-0

A3:A0

Protected Monitoring selection. See

Table 1

,

page 15

.

4-7

reserved

Reserved.

Table 20. Digital Loopback Register, DL (0Ch)

Bit

1

Name

Function

2

7-0

DL7-DL0

Setting a bit to

“

1

”

enables digital loopback for the respective transceiver.

1. On power up all register bits are set to

“

0

”

.

2. During digital loopback LOS and TAOS stay active and independent of TCLK, while data received on

TPOS/TNEG/CKLK is looped back to RPOS/RNEG/RCLK.

Table 21. LOS/AIS Criteria Register, LCS (0Dh)

Bit

1

Name

Function

2

7-0

LCS7-LCS0

T1 Mode

Don

’

t care. T1.231 compliant LOS/AIS detection is used.

E1 Mode

Setting a bit to

“

1

”

selects the ETSI 300233 LOS. Setting a bit to

“

0

”

selects G.775

LOS mode. AIS works correctly for both ETSI and ITU when the bit is cleared to

“

0

”

.

See errata 10.3 or higher for a way to implement ETSI LOS and AIS.

1. On power-on reset the register is set to

“

0

”

.

2. T1 or E1 operation mode is determined by the PSDAT settings.

Table 22. Automatic TAOS Select Register, ATS (0Eh)

Bit

1

Name

Function

7-0

ATS7-ATS0

Setting a bit to

“

1

”

enables automatic TAOS generation whenever a LOS condition is

detected in the respective transceiver.

1. On power-on reset the register is set to

“

0

”

.

2. This feature is not available in data recovery and line driver mode (MCLK= High and TCLK = High).

相关PDF资料 |

PDF描述 |

|---|---|

| LXT384LE | Telecomm/Datacomm |

| LXT386BE | PCM TRANSCEIVER|QUAD|CEPT PCM-30/E-1|CMOS|BGA|160PIN|PLASTIC |

| LXT386LE | PCM TRANSCEIVER|QUAD|CEPT PCM-30/E-1|CMOS|QFP|100PIN|PLASTIC |

| LXT388LE | PCM TRANSCEIVER|DUAL|CEPT PCM-30/E-1|CMOS|QFP|100PIN|PLASTIC |

| LXT400JE | Hermetically Sealed, 3.3V, High Speed, High CMR, Logic Gate Optocoupler |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LXT384LE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecomm/Datacomm |

| LXT386 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:QUAD T1/E1/J1 Transceiver |

| LXT386BE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM TRANSCEIVER|QUAD|CEPT PCM-30/E-1|CMOS|BGA|160PIN|PLASTIC |

| LXT386LE | 制造商:LEVEL1 功能描述: |

| LXT388LE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM TRANSCEIVER|DUAL|CEPT PCM-30/E-1|CMOS|QFP|100PIN|PLASTIC |

发布紧急采购,3分钟左右您将得到回复。