- 您现在的位置:买卖IC网 > PDF目录69009 > M306K9F8LRP 16-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP144 PDF资料下载

参数资料

| 型号: | M306K9F8LRP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP144 |

| 封装: | 16 X 16 MM, 0.40 MM PITCH, PLASTIC, TQFP-144 |

| 文件页数: | 51/101页 |

| 文件大小: | 2590K |

| 代理商: | M306K9F8LRP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页当前第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页

Rev.1.00

Jun 06, 2003

page 36 of 290

M16C/6K9 Group

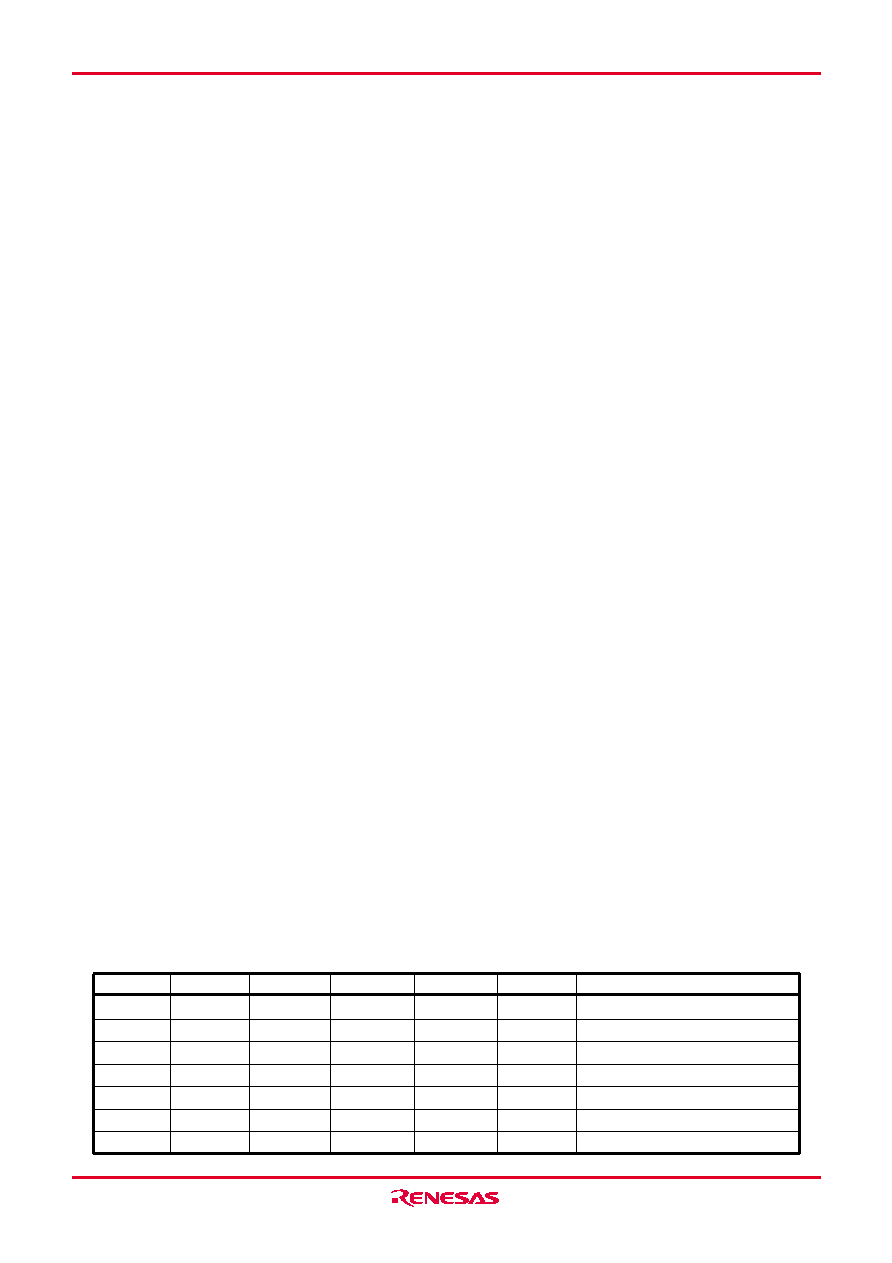

0100

0

Invalid

Division by 2 mode

1000

0

Invalid

Division by 4 mode

Invalid

0

1

0

Invalid

Division by 8 mode

1100

0

Invalid

Division by 16 mode

0000

0

Invalid

No-division mode

Invalid

1

Invalid

0

1

Low-speed mode

Invalid

1

Invalid

1

Low power dissipation mode

Status Transition Of BCLK

Power dissipation can be reduced and low-voltage operation achieved by changing the count source for

BCLK. Table.WA-4 shows the operating modes corresponding to the settings of system clock control regis-

ters 0 and 1.

After a reset, operation defaults to division by 8 mode. When shifting from high speed mode or mid-speed

mode to stop mode, and after a reset main clock division select bit 0 (bit 6 at address 000616) is set to “1”. It

is matained in low speed mode and low power dissipation mode.

(1) Division by 2 mode

The main clock is divided by 2 to obtain the BCLK.

(2) Division by 4 mode

The main clock is divided by 4 to obtain the BCLK.

(3) Division by 8 mode

The main clock is divided by 8 to obtain the BCLK. After reset, it works in this mode. Note that oscillation of

the main clock must have stabilized before transferring from this mode to No-division, Division by 2 and

Division by 4 mode. Oscillation of the sub clock must have stabilized before transferring this mode to Low-

speed mode and Low power dissipation mode.

(4) Division by 16 mode

The main clock is divided by 16 to obtain the BCLK.

(5) No-division mode

The main clock is used as the BCLK.

(6) Low-speed mode

fC is used as the BCLK. Note that oscillation of both the main and sub clocks must have stabilized before

transferring from this mode to another or vice versa. At least 2 to 3 seconds are required after the sub clock

starts. Therefore, the program must be written to wait until this clock has stabilized immediately after power-

ing up and after stop mode is cancelled.

(7) Low power dissipation mode

fC is the BCLK and the main clock is stopped.

Precaution

In the case of switching the BCLK count source from XIN to XCIN, or from XCIN to XIN, it is necessary that the

destination clock count source be stable. The transition should be waited by software after the oscillation

being stable.

CM17

CM16

CM07

CM06

CM05

CM04

Operating mode of BCLK

Table.WA-4 Operating modes dictated by settings of system clock control registers 0 and 1

Status Transition Of BCLK

相关PDF资料 |

PDF描述 |

|---|---|

| M306KAFCLRP | 16-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP144 |

| M306N0MCT-XXXXFP | 16-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP100 |

| M306N5FCTGP | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 |

| M306N5FCFP | 16-BIT, FLASH, 24 MHz, MICROCONTROLLER, PQFP100 |

| M306N5FCVFP | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M306K9FCLRP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M306K9T2-CPE | 功能描述:M-SUPPORT TOOL RoHS:否 类别:编程器,开发系统 >> 内电路编程器、仿真器以及调试器 系列:- 产品变化通告:Development Systems Discontinuation 19/Jul/2010 标准包装:1 系列:* 类型:* 适用于相关产品:* 所含物品:* |

| M306KAFCLRP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER Description |

| M306N0FG | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M306N0FGT | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

发布紧急采购,3分钟左右您将得到回复。