- 您现在的位置:买卖IC网 > PDF目录69010 > M34501M2-XXXFP 4-BIT, MROM, MICROCONTROLLER, PDSO20 PDF资料下载

参数资料

| 型号: | M34501M2-XXXFP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 4-BIT, MROM, MICROCONTROLLER, PDSO20 |

| 封装: | 5.30 X 12.60 MM, 1.27 MM PITCH, PLASTIC, SOP-20 |

| 文件页数: | 32/118页 |

| 文件大小: | 952K |

| 代理商: | M34501M2-XXXFP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页

Rev.3.01

2005.02.07

page 18 of 112

REJ03B0104-0301

4501 Group

INTERRUPT FUNCTION

The interrupt type is a vectored interrupt branching to an individual

address (interrupt address) according to each interrupt source. An

interrupt occurs when the following 3 conditions are satisfied.

An interrupt activated condition is satisfied (request flag = “1”)

Interrupt enable bit is enabled (“1”)

Interrupt enable flag is enabled (INTE = “1”)

Table 3 shows interrupt sources. (Refer to each interrupt request

flag for details of activated conditions.)

(1) Interrupt enable flag (INTE)

The interrupt enable flag (INTE) controls whether the every inter-

rupt enable/disable. Interrupts are enabled when INTE flag is set to

“1” with the EI instruction and disabled when INTE flag is cleared to

“0” with the DI instruction. When any interrupt occurs, the INTE flag

is automatically cleared to “0,” so that other interrupts are disabled

until the EI instruction is executed.

(2) Interrupt enable bit

Use an interrupt enable bit of interrupt control registers V1 and V2

to select the corresponding interrupt or skip instruction.

Table 4 shows the interrupt request flag, interrupt enable bit and

skip instruction.

Table 5 shows the interrupt enable bit function.

(3) Interrupt request flag

When the activated condition for each interrupt is satisfied, the cor-

responding interrupt request flag is set to “1.” Each interrupt

request flag is cleared to “0” when either;

an interrupt occurs, or

the next instruction is skipped with a skip instruction.

Each interrupt request flag is set when the activated condition is

satisfied even if the interrupt is disabled by the INTE flag or its in-

terrupt enable bit. Once set, the interrupt request flag retains set

until a clear condition is satisfied.

Accordingly, an interrupt occurs when the interrupt disable state is

released while the interrupt request flag is set.

If more than one interrupt request flag is set when the interrupt dis-

able state is released, the interrupt priority level is as follows

shown in Table 3.

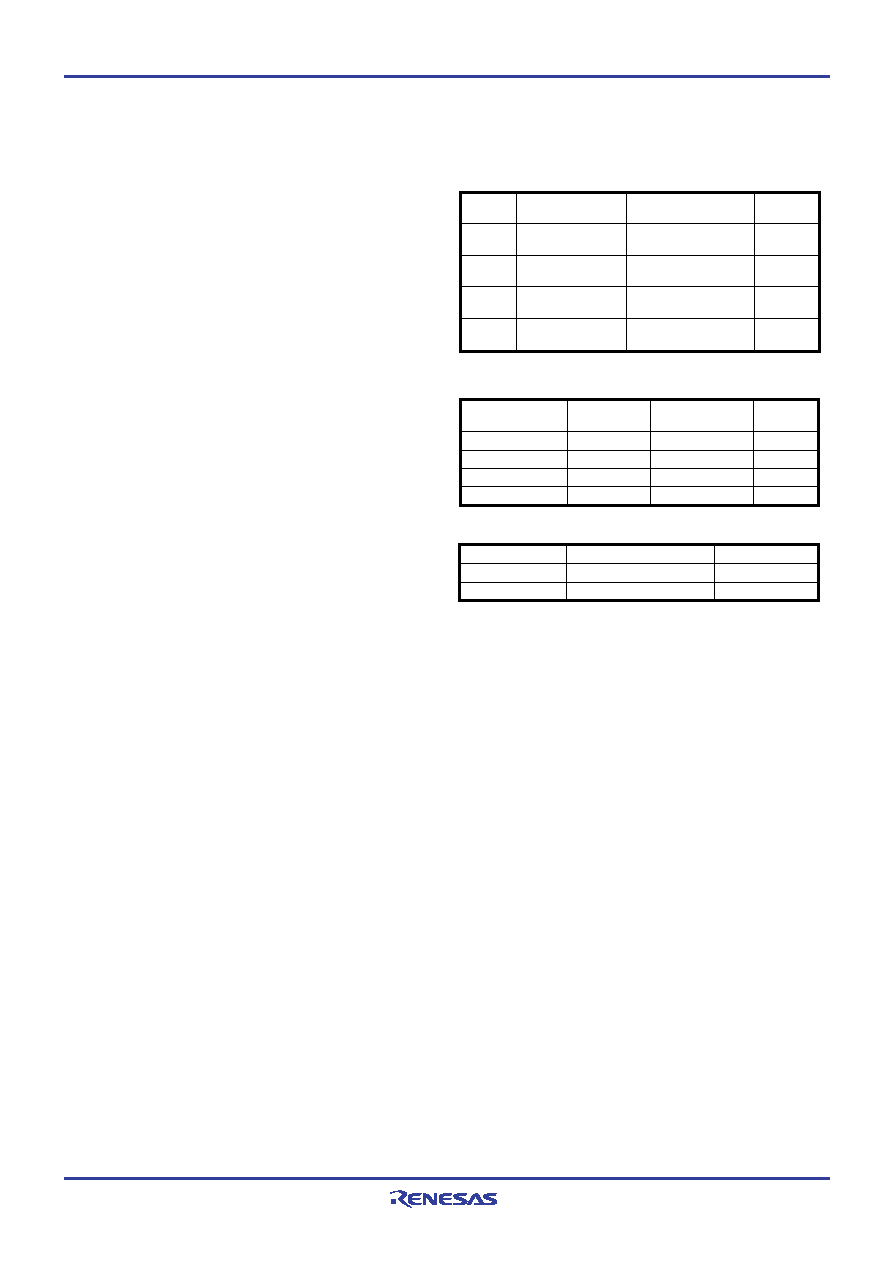

Table 3 Interrupt sources

Activated condition

Level change of INT

pin

Timer 1 underflow

Timer 2 underflow

Completion of

A/D conversion

Priority

level

1

2

3

4

Interrupt name

External 0 interrupt

Timer 1 interrupt

Timer 2 interrupt

A/D interrupt

Table 5 Interrupt enable bit function

Occurrence of interrupt

Enabled

Disabled

Skip instruction

Invalid

Valid

Interrupt enable bit

1

0

Interrupt

address

Address 0

in page 1

Address 4

in page 1

Address 6

in page 1

Address C

in page 1

Table 4 Interrupt request flag, interrupt enable bit and skip in-

struction

Interrupt

request flag

EXF0

T1F

T2F

ADF

Interrupt name

External 0 interrupt

Timer 1 interrupt

Timer 2 interrupt

A/D interrupt

Skip instruction

SNZ0

SNZT1

SNZT2

SNZAD

Interrupt

enable bit

V10

V12

V13

V22

相关PDF资料 |

PDF描述 |

|---|---|

| M34501E4FP | 4-BIT, OTPROM, MICROCONTROLLER, PDSO20 |

| M34501M4-XXXFP | 4-BIT, MROM, MICROCONTROLLER, PDSO20 |

| M34501E4FP | 4-BIT, OTPROM, MICROCONTROLLER, PDSO20 |

| M34502M2-XXXFP | 4-BIT, MROM, MICROCONTROLLER, PDSO24 |

| M34502M4-XXXFP | 4-BIT, MROM, MICROCONTROLLER, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M34501M4 | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34501M4-XXXFP | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34502E4 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34502E4FP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:4-BIT CISC SINGLE-CHIP MICROCOMPUTER 4500 SERIES |

| M34502M2 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

发布紧急采购,3分钟左右您将得到回复。