- 您现在的位置:买卖IC网 > PDF目录80446 > M38D24G6-XXXFP 8-BIT, FLASH, 6.25 MHz, MICROCONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | M38D24G6-XXXFP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 6.25 MHz, MICROCONTROLLER, PQFP64 |

| 封装: | 14 X 14 MM, 0.80 MM PITCH, PLASTIC, LQFP-64 |

| 文件页数: | 58/136页 |

| 文件大小: | 2856K |

| 代理商: | M38D24G6-XXXFP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页当前第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页

Rev.3.02

Apr 10, 2008

Page 28 of 131

REJ03B0177-0302

38D2 Group

<Notes>

The interrupt request bit may be set to “1” in the following cases.

When setting the external interrupt active edge

Related bits: INT0 interrupt edge selection bit

(bit 0 of interrupt edge selection register

(address 003A16))

INT1 interrupt edge selection bit

(bit 1 of interrupt edge selection register)

INT2 interrupt edge selection bit

(bit 2 of interrupt edge selection register)

CNTR0 activate edge switch bit

(bits 6 and 7 of timer X control register 1

(address 002E16))

CNTR1 activate edge switch bit

(bits 6 of timer Y mode register

(address 003816))

When switching the interrupt sources of an interrupt vector

address where two or more interrupt sources are assigned

Related bit:

Timer Y/CNTR1 interrupt switch bit

(bit 3 of interrupt edge selection register)

If it is not necessary to generate an interrupt synchronized with

these settings, take the following sequence.

(1) Set the corresponding enable bit to “0” (disabled).

(2) Set the interrupt edge selection bit (the active edge switch

bit) or the interrupt source bit.

(3) Set the corresponding interrupt request bit to “0” after one

or more instructions have been executed.

(4) Set the corresponding interrupt enable bit to “1” (enabled).

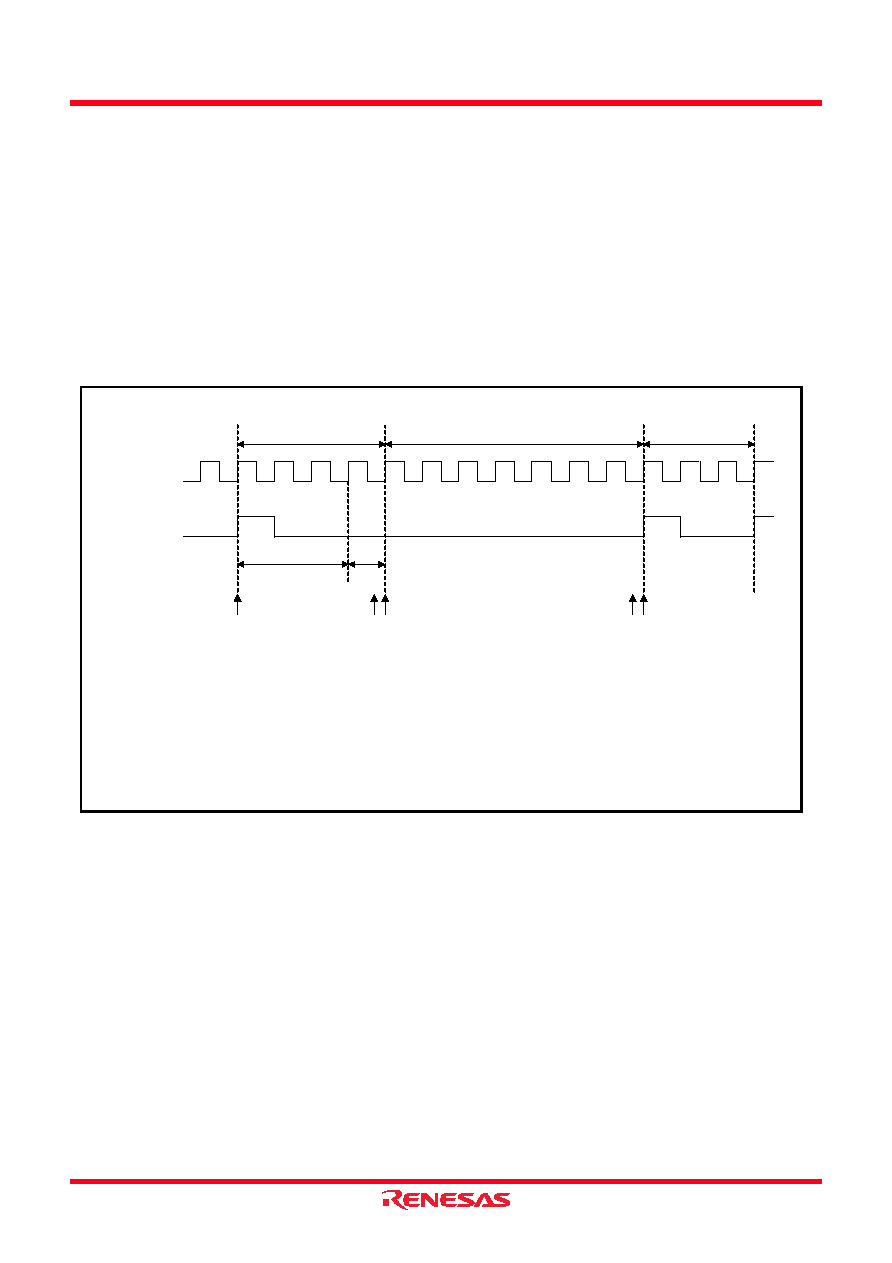

Fig. 20 Timing of interrupt request generation, interrupt request bit, and interrupt acceptance

T1

(1) The interrupt request bit for an interrupt request generated during period 1 is set to “1” at timing point IR1.

(2) The interrupt request bit for an interrupt request generated during period 2 is set to “1” at timing point IR1 or IR2.

The timing point at which the bit is set to “1” varies depending on conditions. When two or more interrupt

requests are generated during the period 2, each request bit may be set to “1” at timing point IR1 or IR2

separately.

T1 T2 T3 : Interrupt acceptance timing points

IR1 IR2 : Timings points at which the interrupt request bit is set to “1”.

Note : Period 2 indicates the last

φ cycle during one instruction cycle.

IR1T2

SYNC

IR2 T3

12

Internal clock

φ

Instruction cycle

Push onto stack

Vector fetch

Instruction cycle

相关PDF资料 |

PDF描述 |

|---|---|

| MC68HC705MC4MS | 8-BIT, UVPROM, 3 MHz, MICROCONTROLLER, CDIP28 |

| MPC8270VRMHBX | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA516 |

| MC9S12HZ64VFU | 16-BIT, FLASH, 25 MHz, MICROCONTROLLER, PQFP80 |

| MC6805P6P | 8-BIT, MROM, 1 MHz, MICROCONTROLLER, PDIP28 |

| MC6805S2P | 8-BIT, MROM, MICROCONTROLLER, PDIP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M38D24G6XXXHP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38D24G7XXXFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38D24G7XXXHP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38D24G8XXXFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38D24G8XXXHP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

发布紧急采购,3分钟左右您将得到回复。