- 您现在的位置:买卖IC网 > PDF目录359091 > M7020R (意法半导体) 32K x 68-bit Entry NETWORK SEARCH ENGINE PDF资料下载

参数资料

| 型号: | M7020R |

| 厂商: | 意法半导体 |

| 英文描述: | 32K x 68-bit Entry NETWORK SEARCH ENGINE |

| 中文描述: | 32K的× 68位进入网络搜索引擎 |

| 文件页数: | 20/150页 |

| 文件大小: | 996K |

| 代理商: | M7020R |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页

M7020R

20/150

Full Out (FULO[1:0]).

FULO[1] and FULO[0] are

the same logical signal. One of these two signals

must be connected to the FULI of up to four down-

stream devices in a depth-cascaded table. Bit [0]

in the data array indicates if the entry is full (1) or

empty (0).This signal is asserted if all of the bits in

the data array are ’1s.’ Refer to Depth-Cascading

to Generate a “FULL” Signal, page 122.

Full Flag (FULL).

When asserted, this signal in-

dicates that the table consisting of many depth-

cascaded devices is full.

Device Identification

Device Identification (ID[4:0]).

The

coded device ID for a depth-cascaded system

starts at 00000 and goes up to 11110. 11111 is re-

served for a special broadcast address that se-

lects all cascaded search engines in the system.

binary-en-

On a broadcast READ-only, the device with the

LDEV bit set to '1' responds.

Supplies

Chip Core Supply (V

DD

).

This is equal to 1.8V.

Chip I/O Supply (V

DDQ

).

This is equal to either

2.5 or 3.3V.

Test Access Port

Test Data In (TDI).

This is the Test Access Port’s

Test Data In.

Test Clock (TCK).

This is the Test Access Port’s

Test Clock.

Test Data Out (TDO).

This is the Test Access

Port’s Test Data Out.

Test Mode Select (TMS).

This is the Test Ac-

cess Port’s Test Mode Select.

Test Reset (TRST_L).

This is the Test Access

Port’s Test Reset.

CLOCKS

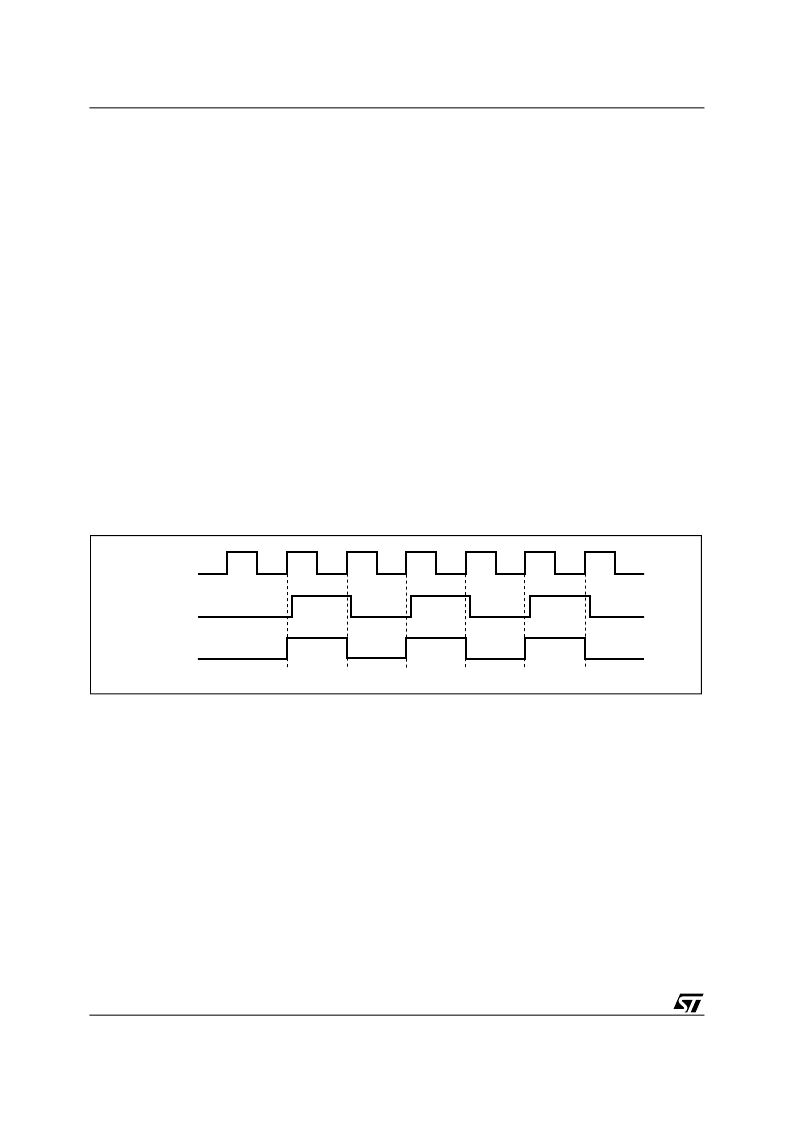

The M7020R receives the CLK2X and PHS_L sig-

nals. It uses the PHS_L signal to divide CLK2X

and generate an internal clock (CLK), as shown in

Figure 9. The M7020R uses CLK2X and CLK for

internal operations.

Figure 9. Clocks (CLK2X and PHS_L)

Note:

Any reference to “CLK Cycles” means 1 cycle of the signal, “CLK.”

1. “CLK” is an internal signal.

CLK2X

PHS_L

CLK(1)

AI04750

相关PDF资料 |

PDF描述 |

|---|---|

| M72DW64000B | 64Mbit (x8/ x16, Multiple Bank, Boot Block) Flash Memory and 16Mbit Pseudo SRAM, 3V Supply, Multiple Memory Product |

| M72DW64000B70ZT | 64Mbit (x8/ x16, Multiple Bank, Boot Block) Flash Memory and 16Mbit Pseudo SRAM, 3V Supply, Multiple Memory Product |

| M72DW64000B90ZT | 64Mbit (x8/ x16, Multiple Bank, Boot Block) Flash Memory and 16Mbit Pseudo SRAM, 3V Supply, Multiple Memory Product |

| M74AC574TTR | OCTAL D-TYPE FLIP FLOP WITH 3 STATE OUTPUT NON INVERTING |

| M74AC574MTR | OCTAL D-TYPE FLIP FLOP WITH 3 STATE OUTPUT NON INVERTING |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M7020R-050ZA1T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:32K x 68-bit Entry NETWORK SEARCH ENGINE |

| M7020R-066ZA1T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:32K x 68-bit Entry NETWORK SEARCH ENGINE |

| M7020R-083ZA1T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:32K x 68-bit Entry NETWORK SEARCH ENGINE |

| M702-230442 | 功能描述:火线接头 IEEE 1394 SMT 4P HORIZONTAL RoHS:否 制造商:Molex 产品:IEEE 1394 Firewire Connectors 标准:IEEE 1394 位置/触点数量:6 节距:2 mm 触点电镀:Unplated 触点材料:Phosphor Bronze 型式:Female 电流额定值:0.5 A 安装风格:Through Hole 端接类型:Solder Tab 连接器类型:Firewire Receptacle |

| M702-230642 | 功能描述:火线接头 IEEE 1394 SMT 6P HORIZONTAL RoHS:否 制造商:Molex 产品:IEEE 1394 Firewire Connectors 标准:IEEE 1394 位置/触点数量:6 节距:2 mm 触点电镀:Unplated 触点材料:Phosphor Bronze 型式:Female 电流额定值:0.5 A 安装风格:Through Hole 端接类型:Solder Tab 连接器类型:Firewire Receptacle |

发布紧急采购,3分钟左右您将得到回复。