- 您现在的位置:买卖IC网 > PDF目录383307 > MA17501 (Dynex Semiconductor Ltd.) Radiation Hard MIL-STD-1750A Execution unit PDF资料下载

参数资料

| 型号: | MA17501 |

| 厂商: | Dynex Semiconductor Ltd. |

| 英文描述: | Radiation Hard MIL-STD-1750A Execution unit |

| 中文描述: | 辐射硬的MIL - STD - 1750A执行单元 |

| 文件页数: | 11/35页 |

| 文件大小: | 431K |

| 代理商: | MA17501 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

MA17501

11/35

4.2 INSTRUCTION EXECUTION

Instruction execution is characterised by a variety of

operations composed of various types of machine cycles. The

Execution Unit contains the clock generation circuitry that

creates the different machine cycles depending on the

particular operation being performed at the time. These

operations include: (1) internal CPU cycles, (2) instruction

fetches, (3) operand transfers, and (4) input/output transfers.

Instruction execution may be interrupted at the end of any

individual machine cycle by the PAUSEN (denoting DMA

operations) clock generation circuitry input, and at the

beginning of any given MIL-STD-1750A instruction by an

(IU)IRN or HOLDN low input to the Control Unit.

4.2.1 Internal CPU Cycles

All CPU data manipulation and housekeeping operations

are performed using internal CPU cycles. Internal CPU cycles

are either five or six OSC periods long and are characterised

by AS low and DSN, (IU)DDN, and M/ION high. Section 5.0

provides timing characteristics for internal CPU cycles.

The majority of lnternal CPU Cycles are five OSC period

machine cycles. Six OSC period machine cycles occur when

executing conditional jump or branch microinstructions; the EU

is calculating the branch condition to determine the state of the

T1 output signal.

4.2.2 Instruction Fetches

lnstruction fetches are used to keep the instruction pipeline

full. This ensures that the next instruction is ready for

execution when the preceding instruction is completed.

During jump and branch instruction execution the pipeline

is flushed, then refilled via two consecutive instruction fetches

starting at the new instruction location. The pipeline is also

refilled as part of the interrupt and Hold processing.

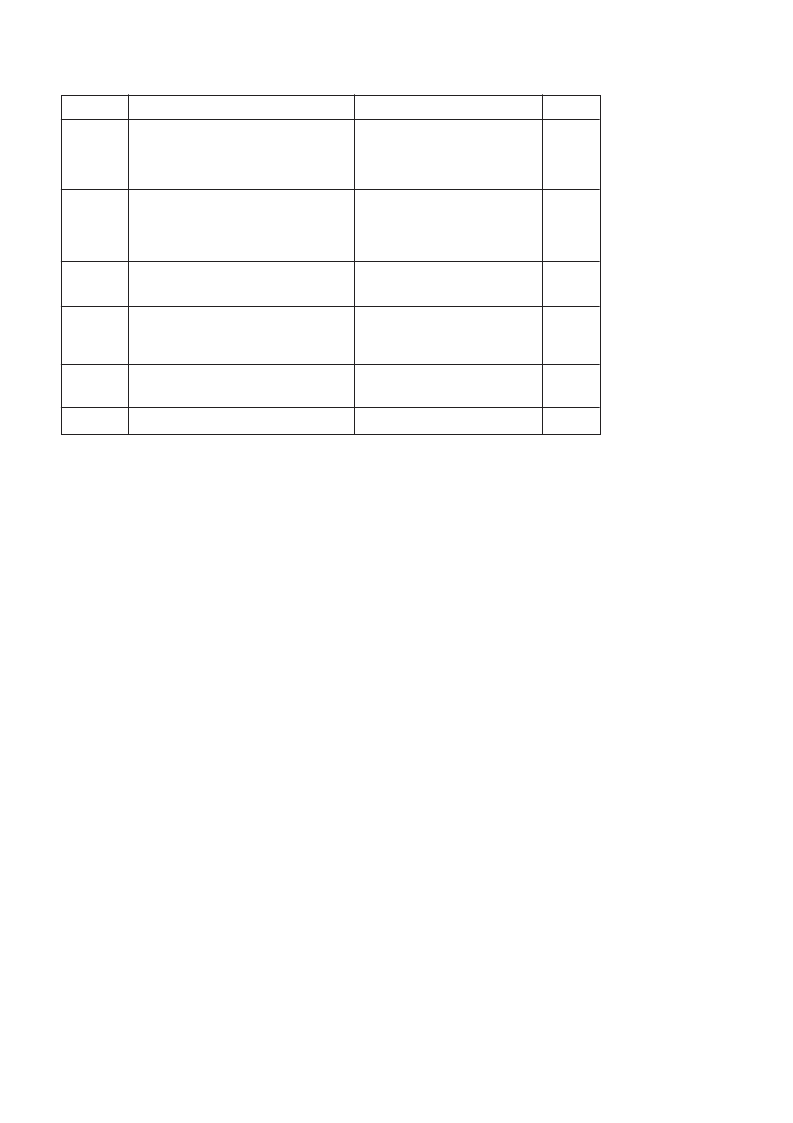

BIT

Test Coverage

BIT Fail Codes (FT

13,14,15

)

Cycles

1

Mlcrocode Sequencer

IB Register Control

Barrel Shifter

Byte Operations and Flags

100

221

2

Temporary Registers (T0 - T7)

Microcode Flags

Multiply

Divide

101

166

3

Interrupt Unit - MK, Pl, FT

Enable/Disable Interrupts

111

214

4

Status Word Control

User Flags

General Registers (R0 - R15

110

154

5

Timer A

Timer B

111

763

-

BIT Pass/Fail Overhead

-

26

Note: BIT pass is indicated by all zeros in FT bits 13, 14, and 15.

Table 2: MAS281 BIT Summary

lnstruction fetches are five (minimum) OSC period

machine cycles characterised by IN/OPN, M/lON, and RD/WN

high. lnstruction fetches use pipeline registers lA and IB, the

instruction counter (lC), and the data input register (Dl).

Assuming an empty instruction pipeline (as a result of a reset,

jump or branch), the contents of lC are placed on the AD Bus

as an address. The returned value (the instruction) is stored in

the IA register. The lC register is incremented (dedicated

counter mode) and the next fetch is performed.

This second returned value, which may be an instruction or

an immediate operand, is stored in both the lA and Dl registers

as the previous contents of IA advance to the IB register to be

decoded into their microcoded routine. If the second returned

value is an immediate operand, a third instruction fetch will

occur with the instruction being loaded into lA only; Dl retains

the immediate operand.

The data portion (SYNCN high) of instruction fetch cycles

can be extended beyond their minimum five OSC periods by

use of the RDYN signal. RDYN held high during the high-to-

low transition of the machine cycles fifth OSC cycle will extend

the data portion of the machine cycle. The machine cycle can

be completed at any succeeding OSC cycle high-to-low

transition by enveloping this OSC edge with RDYN low.

4.2.3 Operand Transfers

Operand transfers are used to obtain operands to be used

by an instruction and to save any results of an instructions

execution. Machine cycles associated with operand transfers

are a minimum of five OSC periods in duration. The RDYN

signal can be used to insert wait states into the data portion of

the machine cycle (SYNCN high) to accommodate slow

memory.

相关PDF资料 |

PDF描述 |

|---|---|

| MA17502 | Radiation Hard MIL-STD-1750A Control Unit |

| MA17503 | Radiation Hard MIL-STD-1750A Interrupt Unit |

| MA1916 | Radiation Hard Reed-Solomon & Convolution Encoder |

| MA28139 | OBDH Bus Terminal |

| MA28140 | Packet Telecommand Decoder |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MA17502 | 制造商:DYNEX 制造商全称:Dynex Semiconductor 功能描述:Radiation Hard MIL-STD-1750A Control Unit |

| MA17503 | 制造商:DYNEX 制造商全称:Dynex Semiconductor 功能描述:Radiation Hard MIL-STD-1750A Interrupt Unit |

| MA1751E12B1+6-FSR-EM | 制造商:Mechatronics Fan Group 功能描述: |

| MA1751E12B-FSR | 功能描述:FAN AXIAL 172X150X51MM 12VDC 制造商:mechatronics fan group 系列:MA1751 零件状态:有效 电压 - 额定:12VDC 大小/尺寸:矩形/圆形 - 172mm 长 x 150mm 高 宽度:50.80mm 气流:269.2 CFM(7.62m3/min) 静压力:0.670 英寸水柱(166.9 Pa) 轴承类型:滚珠 风扇类型:管轴式 特性:- 噪声:61 dB(A) 功率(W):- RPM:3150 RPM 端接:2 引线 侵入防护:- 工作温度:- 认可:UL 额定电流:2.2A 电压范围:- 材料 - 框架:铝 材料 - 刀片:聚对苯二甲酸丁二酯(PBT) 重量:1.6 磅(725.7g) 标准包装:20 |

| MA1751E24B-FSR | 功能描述:AXIAL FAN 172X150X51MM 24VDC 制造商:mechatronics fan group 系列:* 零件状态:在售 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。