- 您现在的位置:买卖IC网 > PDF目录9882 > MAX1148BEUP+T (Maxim Integrated Products)IC ADC 14BIT 116KSPS 20-TSSOP PDF资料下载

参数资料

| 型号: | MAX1148BEUP+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 5/25页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT 116KSPS 20-TSSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 位数: | 14 |

| 采样率(每秒): | 116k |

| 数据接口: | MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 879mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 8 个单端,单极;8 个单端,双极;4 个差分,单极;4 个差分,双极 |

MAX1146–MAX1149

Multichannel, True-Differential,

Serial, 14-Bit ADCs

______________________________________________________________________________________

13

Input Bandwidth

The MAX1146–MAX1149 feature input tracking circuitry

with a 3.0MHz small-signal bandwidth. The 3.0MHz

input bandwidth makes it possible to digitize high-

speed transient events and measure periodic signals

with bandwidths exceeding the ADC’s sampling rate by

using undersampling techniques. To avoid high fre-

quency signals being aliased into the frequency band

of interest, anti-alias filtering is recommended.

Analog Input Protection

Internal protection diodes clamp the analog input to

VDD and AGND. These diodes allow the analog inputs

to swing from (AGND - 0.3V) to (VDD + 0.3V) without

causing damage to the device. For accurate conver-

sions, the inputs must not go more than 50mV below

AGND or above VDD.

Note: If the analog input exceeds 50mV beyond the sup-

ply rails, limit the current to 2mA.

Quick Look

Use the circuit of Figure 7 to quickly evaluate the

MAX1148/MAX1149. The MAX1148/MAX1149 require a

control byte to be written to DIN using SCLK before

each conversion. Connecting DIN to VDD and clocking

SCLK feeds in a control byte of $FF HEX (see Table 1).

Trigger single-ended unipolar conversions on CH7 in

external clock mode without powering down between

conversions. In external clock mode, the SSTRB output

pulses high for two clock periods before the MSB of the

14-bit conversion result is shifted out of DOUT. Varying

the analog input to CH7 alters the sequence of bits

from DOUT. A total of 18 clock cycles are required per

conversion (Figure 10). All transitions of the SSTRB and

DOUT outputs occur on the falling edge of SCLK.

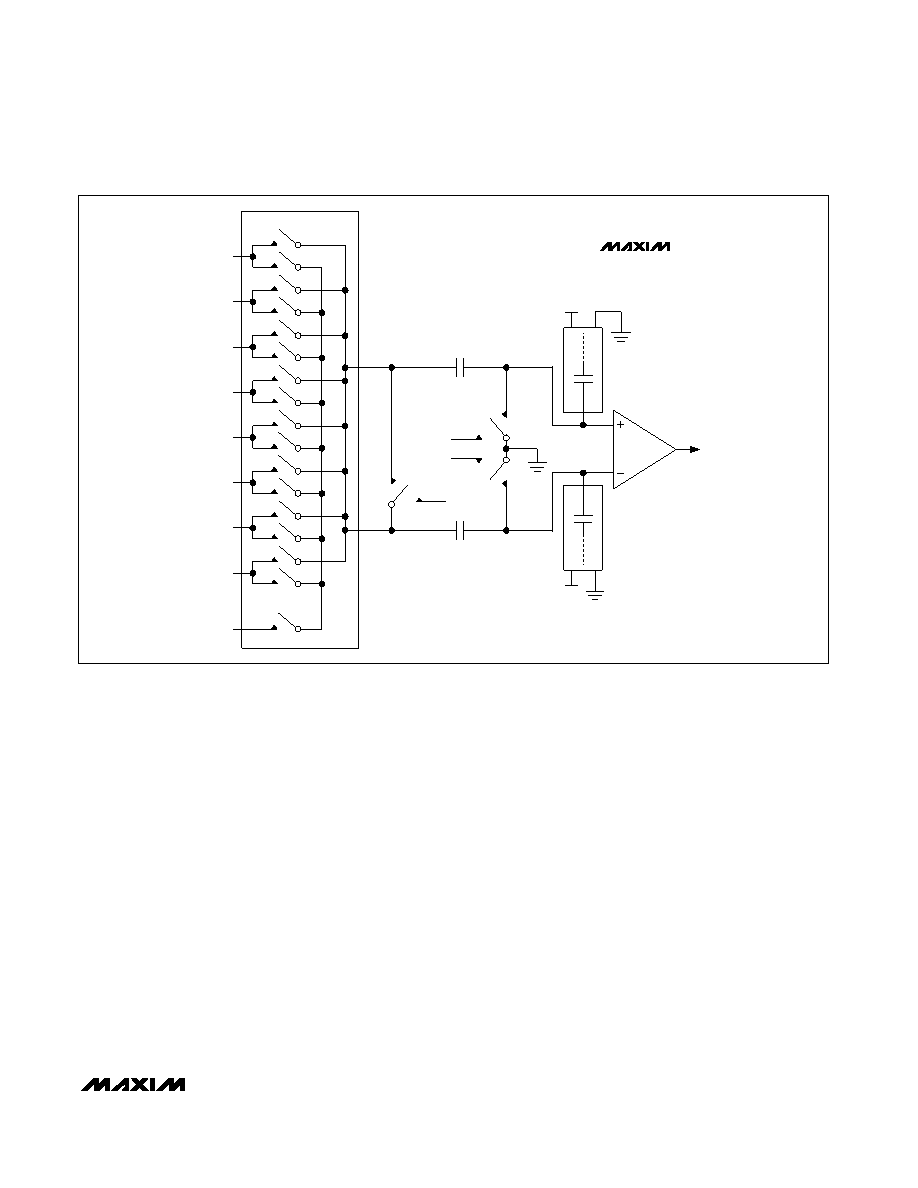

MAX1148

MAX1149

CH0

ANALOG INPUT MUX

CH1

CH2

CH3

CH4

CH5

CH6

CH7

COM

IN+

IN-

TRACK

HOLD

CT/H+

CT/H-

TRACK

REF

14-BIT

CAPACITIVE

DAC

14-BIT

CAPACITIVE

DAC

REF

HOLD

Figure 6. Equivalent Input Circuit

相关PDF资料 |

PDF描述 |

|---|---|

| MAX158BCAI+T | IC ADC 8BIT 8CH W/MUX&REF 28SSOP |

| MAX1297AEEG+T | IC ADC 12BIT 265KSPS 24-QSOP |

| MAX1296AEEG+T | IC ADC 12BIT 420KSPS 24-QSOP |

| MAX1268AEEG+T | IC ADC 12BIT 420KSPS 24-QSOP |

| MAX1267AEEG+T | IC ADC 12BIT 265KSPS 24-QSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX1148CGP | 制造商:Maxim Integrated Products 功能描述:MULTICHANNEL, TRUE-DIFFERENTIAL, SERIAL, 14-B - Rail/Tube |

| MAX1148CUP | 制造商:Maxim Integrated Products 功能描述:MULTICHANNEL, TRUE-DIFFERENTIAL, SERIAL, 14-B - Rail/Tube |

| MAX1148EGP | 制造商:Maxim Integrated Products 功能描述:MULTICHANNEL, TRUE-DIFFERENTIAL, SERIAL, 14-B - Rail/Tube |

| MAX1148EUP | 制造商:Maxim Integrated Products 功能描述:MULTICHANNEL, TRUE-DIFFERENTIAL, SERIAL, 14-B - Rail/Tube |

| MAX1149 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Multichannel, True-Differential, Serial, 14-Bit ADCs |

发布紧急采购,3分钟左右您将得到回复。