参数资料

| 型号: | MAX9856ETL+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 18/46页 |

| 文件大小: | 0K |

| 描述: | IC AUDIO CODEC 40TQFN-EP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 类型: | 音频编解码器 |

| 数据接口: | 串行 |

| 分辨率(位): | 18 b |

| ADC / DAC 数量: | 2 / 2 |

| 三角积分调变: | 是 |

| S/N 比,标准 ADC / DAC (db): | 77 / 91 |

| 动态范围,标准 ADC / DAC (db): | 85 / 91 |

| 电压 - 电源,模拟: | 1.71 V ~ 3.6 V |

| 电压 - 电源,数字: | 1.71 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-WFQFN 裸露焊盘 |

| 供应商设备封装: | 40-TQFN-EP(5x5) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

MAX9856

Low-Power Audio CODEC with

DirectDrive Headphone Amplifiers

______________________________________________________________________________________

25

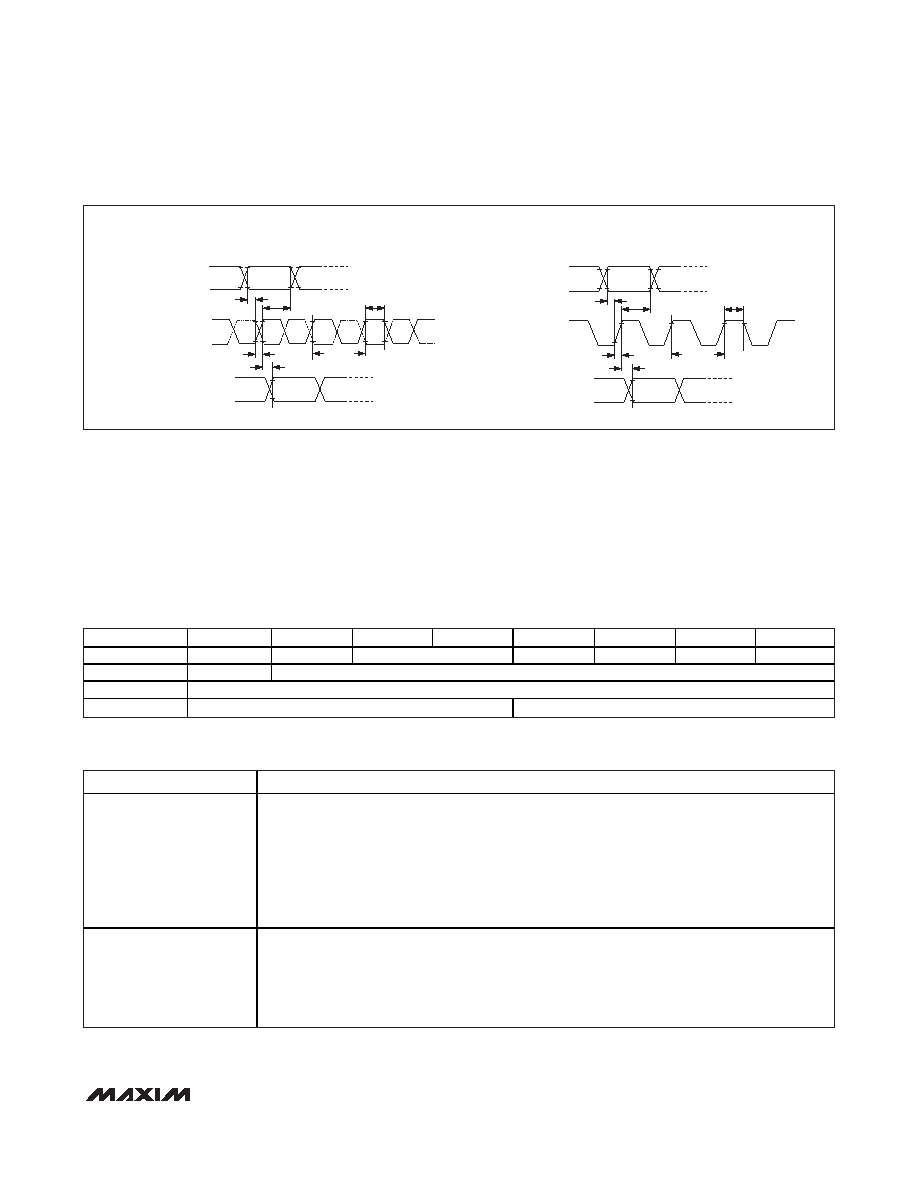

ADC Interface

The stereo ADC is capable of outputting data at any

sample rate from 8kHz to 48kHz. Data can be output in

common formats including left justified, I2S, and PCM

(Figure 1). Figure 2 shows the digital timing in both

slave and master modes.

If the DAC and ADC operate at the same sample rate

only the LRCLK_D is needed, allowing the LRCLK_A

pin to be reassigned as a GPIO. When configured as a

general-purpose output, LRCLK_A can be set high or

low by the APIN bits. When configured as a general-

purpose input, the status is reported in register 0x00.

Table 7 lists and describes the ADC interface registers.

DAI STEREO SERIAL INTERFACE TIMING DIAGRAM (SLAVE MODE)

DAI STEREO SERIAL INTERFACE TIMING DIAGRAM (MASTER MODE)

SDIN/LRCLK (INPUTS)

BCLK (BCI = 0, INPUT)

BCLK (BCI = 1, INPUT)

SDOUT (OUTPUT)

SDIN (INPUT)

BCLK (OUTPUT)

SDOUT/LRCLK (OUTPUTS)

tSU

tr, tf

tHD

tDLY

tBCLKS

tBCLKM

tBCLKH, tBCLKL

Figure 2. Digital Audio Interface Timing Diagrams

REG

B7

B6

B5

B4

B3

B2

B1

B0

0x07

AWCI

ABCI

APIN

ADLY

0

0x08

APLLEN

ADCNI[14:8]

0x09

ADCNI[7:0]

0x0A

AGAIN

ANTH

Table 7. ADC Interface Registers

REGISTER

FUNCTION

AWCI

ADC Word Clock (LRCLK_A) Invert

When PCM = 0:

0—Left-channel data is transmitted while LRCLK_A is low.

1—Right-channel data is transmitted while LRCLK_A is low.

When PCM = 1:

0—Start of a new frame is signified by the falling edge of the LRCLK_A pulse.

1—Start of a new frame is signified by the rising edge of the LRCLK_A pulse.

ABCI

ADC BCLK Invert:

0—SDOUT is valid on the rising edge of BCLK.

1—SDOUT is valid on the falling edge of BCLK.

If operating in master mode, the ABCI bit has no effect. The DBCI bit controls BCLK to LRCLK_A

timing.

ADC Interface Register Bit Description

相关PDF资料 |

PDF描述 |

|---|---|

| MAX9860ETG+T | IC CODEC MONO AUD 16BIT 24TQFN |

| MAX9867ETJ+T | IC STEREO AUD CODEC LP 32TQFN-EP |

| MAX9880AETM+ | IC CODEC AUDIO STEREO 48TQFN |

| MB86064PB-GE1 | DAC 14BIT 1GSA/S DUAL 12-EFBGA |

| MC100EL1648MELG | IC OSC VCO 1.1GHZ 14SOEIAJ |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9856EVKIT+ | 功能描述:音频 IC 开发工具 Evaluation Kit for the MAX9856 RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| MAX9856GTL/V+ | 功能描述:接口—CODEC Low-Power Audio CODEC with DirectDrive Headphone Amplifiers RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| MAX9856GTL/V+T | 功能描述:接口—CODEC Low-Power Audio CODEC with DirectDrive Headphone Amplifiers RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| MAX985EBT+T | 功能描述:校验器 IC Single uPower Comparator RoHS:否 制造商:STMicroelectronics 产品: 比较器类型: 通道数量: 输出类型:Push-Pull 电源电压-最大:5.5 V 电源电压-最小:1.1 V 补偿电压(最大值):6 mV 电源电流(最大值):1350 nA 响应时间: 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:SC-70-5 封装:Reel |

| MAX985EBT+TG45 | 功能描述:校验器 IC Single uPower Comparator RoHS:否 制造商:STMicroelectronics 产品: 比较器类型: 通道数量: 输出类型:Push-Pull 电源电压-最大:5.5 V 电源电压-最小:1.1 V 补偿电压(最大值):6 mV 电源电流(最大值):1350 nA 响应时间: 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:SC-70-5 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。