- 您现在的位置:买卖IC网 > PDF目录80382 > MB9AF314MPMC 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PQFP80 PDF资料下载

参数资料

| 型号: | MB9AF314MPMC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PQFP80 |

| 封装: | 0.50 MM PITCH, PLASTIC, LQFP-80 |

| 文件页数: | 29/114页 |

| 文件大小: | 1357K |

| 代理商: | MB9AF314MPMC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页

21

ATmega48PA/88PA/168PA [DATASHEET]

9223F–AVR–04/14

Bit 3 – EERIE: EEPROM Ready Interrupt Enable

Writing EERIE to one enables the EEPROM ready interrupt if the I bit in SREG is set. Writing EERIE to zero disables the

interrupt. The EEPROM ready interrupt generates a constant interrupt when EEPE is cleared. The interrupt will not be

generated during EEPROM write or SPM.

Bit 2 – EEMPE: EEPROM Master Write Enable

The EEMPE bit determines whether setting EEPE to one causes the EEPROM to be written. When EEMPE is set, setting

EEPE within four clock cycles will write data to the EEPROM at the selected address If EEMPE is zero, setting EEPE will

have no effect. When EEMPE has been written to one by software, hardware clears the bit to zero after four clock cycles.

See the description of the EEPE bit for an EEPROM write procedure.

Bit 1 – EEPE: EEPROM Write Enable

The EEPROM write enable signal EEPE is the write strobe to the EEPROM. When address and data are correctly set up,

the EEPE bit must be written to one to write the value into the EEPROM. The EEMPE bit must be written to one before a

logical one is written to EEPE, otherwise no EEPROM write takes place. The following procedure should be followed when

writing the EEPROM (the order of steps 3 and 4 is not essential):

1.

Wait until EEPE becomes zero.

2.

Wait until SELFPRGEN in SPMCSR becomes zero.

3.

Write new EEPROM address to EEAR (optional).

4.

Write new EEPROM data to EEDR (optional).

5.

Write a logical one to the EEMPE bit while writing a zero to EEPE in EECR.

6.

Within four clock cycles after setting EEMPE, write a logical one to EEPE.

The EEPROM can not be programmed during a CPU write to the flash memory. The software must check that the flash

programming is completed before initiating a new EEPROM write. Step 2 is only relevant if the software contains a boot

loader allowing the CPU to program the flash. If the flash is never being updated by the CPU, step 2 can be omitted. See

Section 27. “Boot Loader Support – Read-While-Write Self-Programming” on page 237 for details about Boot programming.

Caution:

An interrupt between step 5 and step 6 will make the write cycle fail, since the EEPROM master write enable

will time-out. If an interrupt routine accessing the EEPROM is interrupting another EEPROM access, the EEAR

or EEDR register will be modified, causing the interrupted EEPROM access to fail. It is recommended to have

the global interrupt flag cleared during all the steps to avoid these problems.

When the write access time has elapsed, the EEPE bit is cleared by hardware. The user software can poll this bit and wait

for a zero before writing the next byte. When EEPE has been set, the CPU is halted for two cycles before the next instruction

is executed.

Bit 0 – EERE: EEPROM Read Enable

The EEPROM read enable signal EERE is the read strobe to the EEPROM. When the correct address is set up in the EEAR

register, the EERE bit must be written to a logic one to trigger the EEPROM read. The EEPROM read access takes one

instruction, and the requested data is available immediately. When the EEPROM is read, the CPU is halted for four cycles

before the next instruction is executed.

The user should poll the EEPE bit before starting the read operation. If a write operation is in progress, it is neither possible

to read the EEPROM, nor to change the EEAR register.

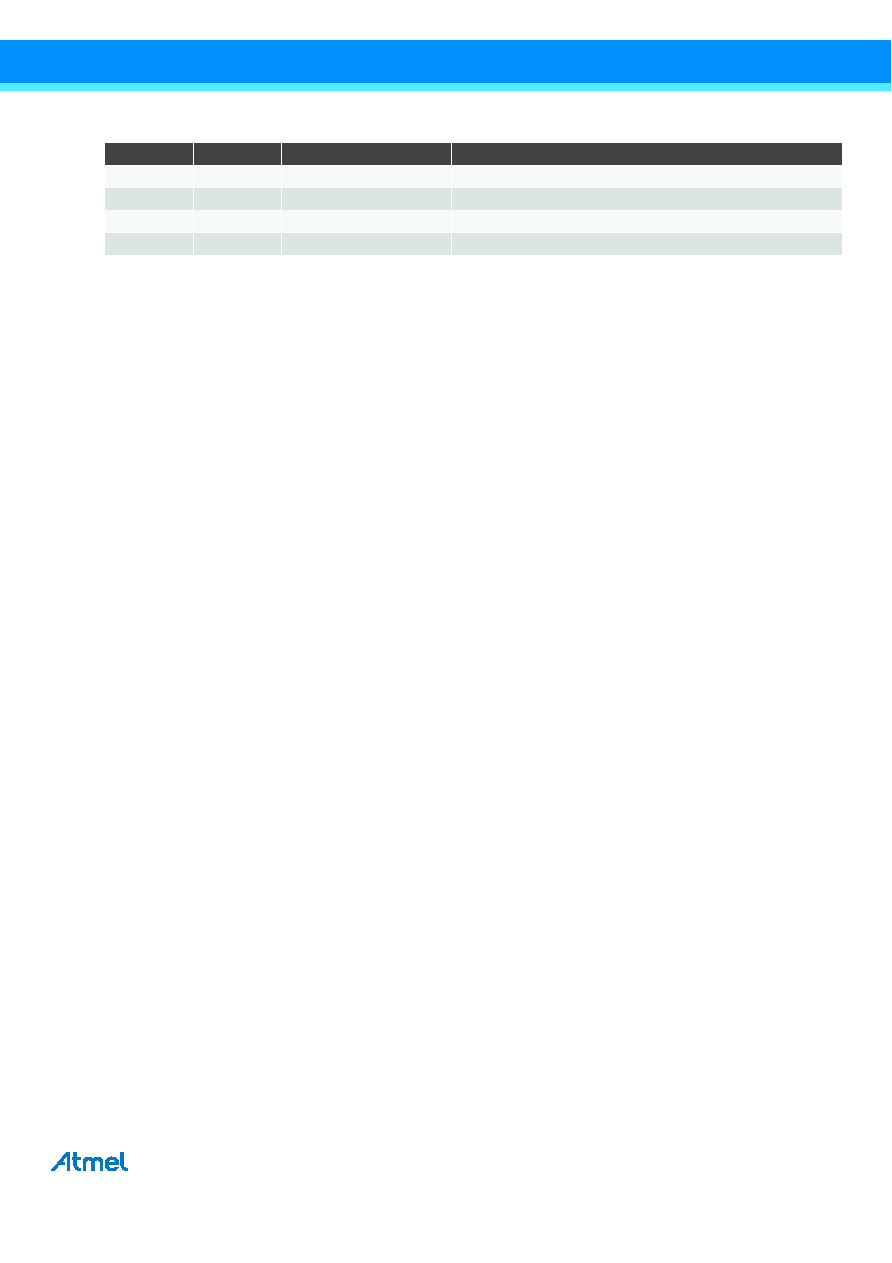

Table 8-1.

EEPROM Mode Bits

EEPM1

EEPM0

Programming Time

Operation

0

3.4ms

Erase and write in one operation (atomic operation)

0

1

1.8ms

Erase only

1

0

1.8ms

Write only

1

–

Reserved for future use

相关PDF资料 |

PDF描述 |

|---|---|

| MB89537APV4 | 8-BIT, MROM, 12.5 MHz, MICROCONTROLLER, PBCC64 |

| M38062E6GP | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| MSM80C31F-GS-VIK | 8-BIT, 12 MHz, MICROCONTROLLER, PQFP44 |

| MSM83C154-1GS-K | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| MC68HC11A8CFU1 | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MB9AF314MPMC-G-JNE1 | 制造商:FUJITSU 功能描述:MCU 32BIT CORTEX-M3 FM3 80LQFP |

| MB9AF314NABGL-GE1 | 制造商:FUJITSU 功能描述: |

| MB9AF314NAPF-G-JNE1 | 功能描述:IC MCU 32BIT 256KB FLASH 100QFP 制造商:cypress semiconductor corp 系列:FM3 MB9A310A 包装:托盘 零件状态:在售 核心处理器:ARM? Cortex?-M3 核心尺寸:32-位 速度:40MHz 连接性:CSIO,EBI/EMI,I2C,LIN,UART/USART,USB 外设:DMA,LVD,POR,PWM,WDT I/O 数:83 程序存储容量:256KB(256K x 8) 程序存储器类型:闪存 EEPROM 容量:- RAM 容量:32K x 8 电压 - 电源(Vcc/Vdd):2.7 V ~ 5.5 V 数据转换器:A/D 16x12b 振荡器类型:内部 工作温度:-40°C ~ 105°C(TA) 封装/外壳:100-BQFP 供应商器件封装:100-PQFP(20x14) 标准包装:66 |

| MB9AF314NAPMC-G-JNE2 | 功能描述:ARM? Cortex?-M3 FM3 MB9A310A Microcontroller IC 32-Bit 40MHz 256KB (256K x 8) FLASH 100-LQFP (14x14) 制造商:cypress semiconductor corp 系列:FM3 MB9A310A 包装:托盘 零件状态:有效 核心处理器:ARM? Cortex?-M3 核心尺寸:32-位 速度:40MHz 连接性:CSIO,EBI/EMI,I2C,LIN,UART/USART,USB 外设:DMA,LVD,POR,PWM,WDT I/O 数:83 程序存储容量:256KB(256K x 8) 程序存储器类型:闪存 EEPROM 容量:- RAM 容量:32K x 8 电压 - 电源(Vcc/Vdd):2.7 V ~ 5.5 V 数据转换器:A/D 16x12b 振荡器类型:内部 工作温度:-40°C ~ 105°C(TA) 封装/外壳:100-LQFP 供应商器件封装:100-LQFP(14x14) 标准包装:90 |

| MB9AF314NBGL-GE1 | 制造商:FUJITSU 功能描述: 制造商:FUJITSU 功能描述:MCU 32BIT CORTEX-M3 FM3 112BGA 制造商:FUJITSU 功能描述:MCU, 32BIT, CORTEX-M3, FM3, 112BGA 制造商:FUJITSU 功能描述:MCU, 32BIT, CORTEX-M3, FM3, 112BGA, Controller Family/Series:ARM Cortex-M3, Core 制造商:FUJITSU 功能描述:MCU, 32BIT, CORTEX-M3, FM3, 112BGA, Controller Family/Series:ARM Cortex-M3, Core Size:32bit, No. of I/O's:83, Supply Voltage Min:2.7V, Supply Voltage Max:5.5V, Digital IC Case Style:BGA, No. of Pins:112, Program Memory Size:256KB, , RoHS Compliant: Yes |

发布紧急采购,3分钟左右您将得到回复。