- 您现在的位置:买卖IC网 > PDF目录69028 > MC16S2CPU20B1 (FREESCALE SEMICONDUCTOR INC) 16-BIT, 20.97 MHz, MICROCONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | MC16S2CPU20B1 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, 20.97 MHz, MICROCONTROLLER, PQFP100 |

| 封装: | TQFP-100 |

| 文件页数: | 25/104页 |

| 文件大小: | 812K |

| 代理商: | MC16S2CPU20B1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

MC68HC16S2

MOTOROLA

MC68HC16S2TS/D

27

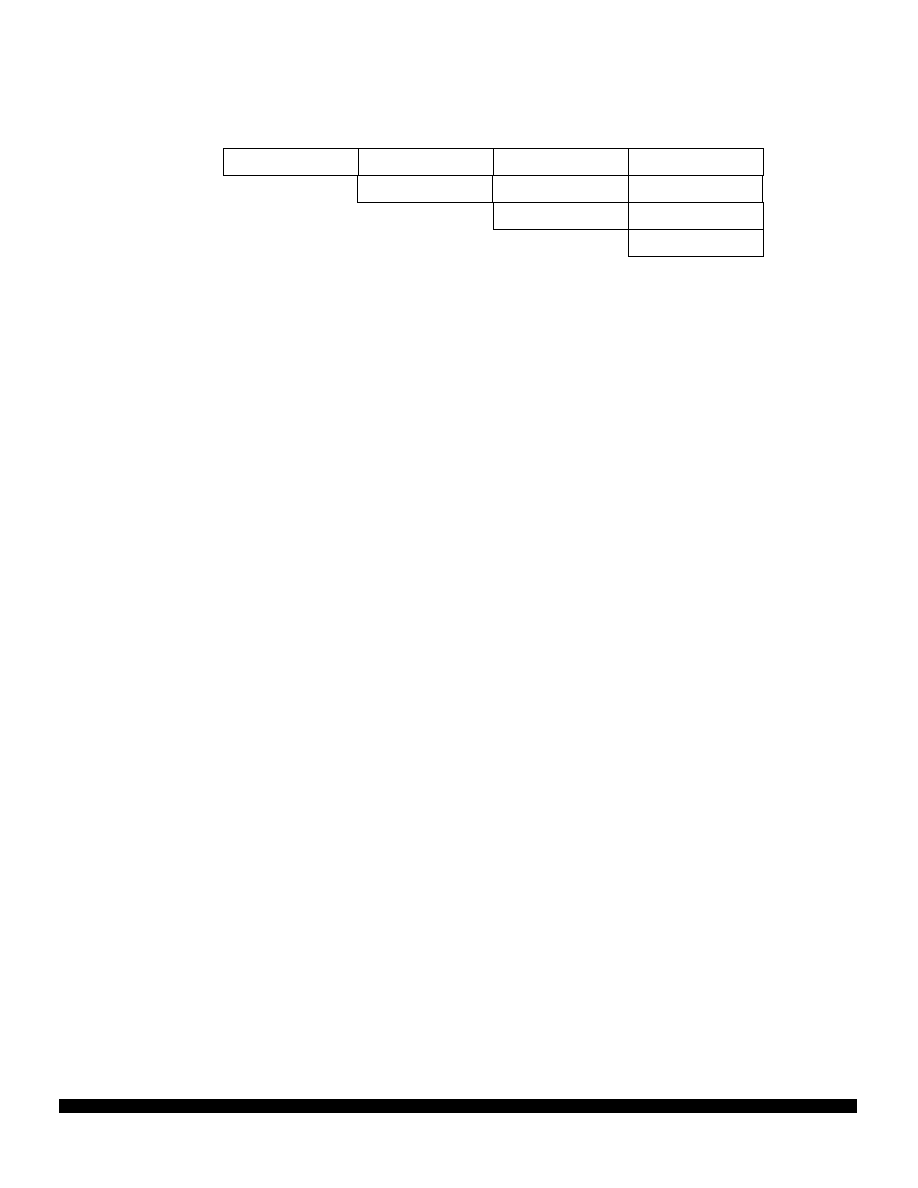

Figure 10 Operand Byte Order

3.5.9 Operand Alignment

The data multiplexer establishes the necessary connections for different combinations of address and

data sizes. The multiplexer takes the two bytes of the 16-bit bus and routes them to their required po-

sitions. Positioning of bytes is determined by the size and address outputs. SIZ1 and SIZ0 indicate the

remaining number of bytes to be transferred during the current bus cycle. The number of bytes trans-

ferred is equal to or less than the size indicated by SIZ1 and SIZ0, depending on port width.

ADDR0 also affects the operation of the data multiplexer. During an operand transfer, ADDR[23:1]

indicate the word base address of the portion of the operand to be accessed, and ADDR0 indicates the

byte offset from the base. Bear in mind the fact that ADDR[23:20] follow the state of ADDR19 in the

MC68HC16S2.

3.5.10 Misaligned Operands

CPU16 processor architecture uses a basic operand size of 16 bits. An operand is misaligned when it

overlaps a word boundary. This is determined by the value of ADDR0. When ADDR0 = 0 (an even ad-

dress), the address is on a word and byte boundary. When ADDR0 = 1 (an odd address), the address

is on a byte boundary only. A byte operand is aligned at any address; a word or long-word operand is

misaligned at an odd address.

The largest amount of data that can be transferred by a single bus cycle is an aligned word. If the MCU

transfers a long-word operand via a 16-bit port, the most significant operand word is transferred on the

first bus cycle and the least significant operand word on a following bus cycle.

The CPU16 can perform misaligned word transfers. This capability makes it software compatible with

the M68HC11 CPU. The CPU16 treats misaligned long-word transfers as two misaligned word trans-

fers.

3.5.11 Operand Transfer Cases

Table 16 summarizes how operands are aligned for various types of transfers. OPn entries are portions

of a requested operand that are read or written during a bus cycle and are defined by SIZ1, SIZ0, and

ADDR0 for that bus cycle.

OP0

OPERAND BYTE ORDER

OP1

OP2

OP3

24

31

23

16 15

8 7

0

BYTE ORDER

OPERAND

LONG WORD

THREE BYTE

WORD

BYTE

OP2

OP1

OP0

OP1

OP0

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

..

.

相关PDF资料 |

PDF描述 |

|---|---|

| MC68HC16X1CTH | 16-BIT, MROM, 16.78 MHz, MICROCONTROLLER, PQFP120 |

| MC68HC24VP | 16 I/O, PIA-GENERAL PURPOSE, PDIP40 |

| MC68HC33CFG | 48 I/O, PIA-GENERAL PURPOSE, PQFP100 |

| MC68HC33FG | 48 I/O, PIA-GENERAL PURPOSE, PQFP100 |

| MC68HC56FN | 1 CHANNEL(S), LOCAL AREA NETWORK CONTROLLER, PQCC28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC16XSD200FK | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Dual 16 mOhm High Side Switch |

| MC16Z1CFC25B1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC16Z1CPV20B1 | 制造商:Rochester Electronics LLC 功能描述:16 BIT MCU, 1K RAM - Bulk |

| MC16Z3BCAG16 | 功能描述:16位微控制器 - MCU 16BIT MCU 4KRAM 8KROM RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT |

| MC-17 | 功能描述:TERM BARRIER 17CIRC DUAL ROW RoHS:是 类别:连接器,互连式 >> 接线座 - 隔板块 系列:M 标准包装:10 系列:Beau™ 38780 端接块类型:阻隔块 电路数:15 导线入口数目:30 间距:0.438"(11.12mm) 行数:2 电流:15A 电压:300V 线规:14-22 AWG 顶部端子:螺钉 底部端子:焊片 阻挡层类型:双壁(双) 特点:法兰 颜色:黑 包装:散装 安装类型:通孔 工作温度:- 材料 - 绝缘体:聚对苯二甲酸丁二酯(PBT),玻璃纤维增强型 材料可燃性额定值:UL94 V-0 其它名称:038780-111538780-1115387801115 |

发布紧急采购,3分钟左右您将得到回复。