- 您现在的位置:买卖IC网 > PDF目录69028 > MC16S2CPU20B1 (FREESCALE SEMICONDUCTOR INC) 16-BIT, 20.97 MHz, MICROCONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | MC16S2CPU20B1 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, 20.97 MHz, MICROCONTROLLER, PQFP100 |

| 封装: | TQFP-100 |

| 文件页数: | 81/104页 |

| 文件大小: | 812K |

| 代理商: | MC16S2CPU20B1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页当前第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

MOTOROLA

MC68HC16S2

78

MC68HC16S2TS/D

NOTES:

1. The base configuration of the MC68HC16S2 requires a 32.768 kHz reference.

2. All internal registers retain data at 0 Hz.

3. Assumes that stable VDDSYN is applied, and that the crystal oscillator is stable. Lock time is measured from

the time VDD and VDDSYN are valid until RESET is released. This specification also applies to the period re-

quired for PLL lock after changing the W and Y frequency control bits in the synthesizer control register (SYN-

CR) while the PLL is running, and to the period required for the clock to lock after LPSTOP.

4. This parameter is periodically sampled rather than 100% tested.

5. Assumes that a low-leakage external filter network is used to condition clock synthesizer input voltage. Total

external resistance from the XFC pin due to external leakage must be greater than 15 M

to guarantee this

specification. Filter network geometry can vary depending upon operating environment.

6. Proper layout procedures must be followed to achieve specifications.

7. Internal VCO frequency (fVCO) is determined by SYNCR W and Y bit values.

The SYNCR X bit controls a divide-by-two circuit that is not in the synthesizer feedback loop.

When X = 0, the divider is enabled, and fsys = fVCO ÷ 4.

When X = 1, the divider is disabled, and fsys = fVCO ÷ 2.

X must equal one when operating at maximum specified fsys.

8. Jitter is the average deviation from the programmed frequency measured over the specified interval at max-

imum fsys. Measurements are made with the device powered by filtered supplies and clocked by a stable ex-

ternal clock signal. Noise injected into the PLL circuitry via VDDSYN and VSS and variation in crystal oscillator

frequency increase the Jclk percentage for a given interval. When clock jitter is a critical constraint on control

system operation, this parameter should be measured during functional testing of the final system.

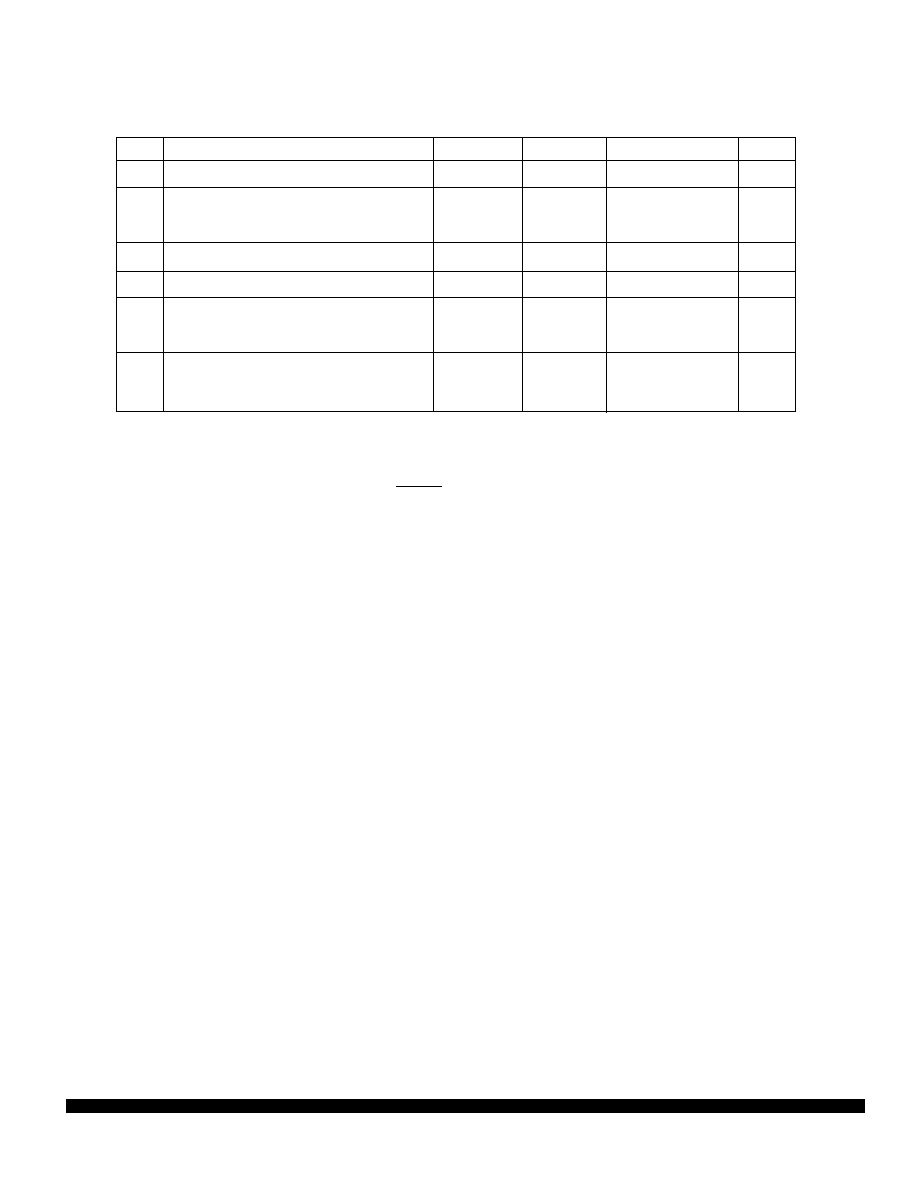

Table 42 20.97 MHz Clock Control Timing

(V

DD

and V

DDSYN

= 5.0 Vdc, V

SS

= 0 Vdc, T

A

= T

L

to T

H

)

Num

Characteristic

Symbol

Min

Max

Unit

1

PLL Reference Frequency Range1

f

ref

20

50

kHz

2

System Frequency2

On-Chip PLL System Frequency Range

External Clock Operation

f

sys

dc

4fref

dc

20.97

MHz

3

PLL Lock Time1, 3, 4, 5, 6

t

lpll

—

20

ms

4

VCO Frequency7

fVCO

—

2 (fsys max)

MHz

5

Limp Mode Clock Frequency

SYNCR X bit = 0

SYNCR X bit = 1

f

limp

—

(f

sys

max)/2

f

sys

max

MHz

6

CLKOUT Jitter1, 4, 5, 6, 8

Short term (5

s interval)

Long term (500

s interval)

J

clk

– 1.5

– 0.5

1.0

0.5

%

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

..

.

相关PDF资料 |

PDF描述 |

|---|---|

| MC68HC16X1CTH | 16-BIT, MROM, 16.78 MHz, MICROCONTROLLER, PQFP120 |

| MC68HC24VP | 16 I/O, PIA-GENERAL PURPOSE, PDIP40 |

| MC68HC33CFG | 48 I/O, PIA-GENERAL PURPOSE, PQFP100 |

| MC68HC33FG | 48 I/O, PIA-GENERAL PURPOSE, PQFP100 |

| MC68HC56FN | 1 CHANNEL(S), LOCAL AREA NETWORK CONTROLLER, PQCC28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC16XSD200FK | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Dual 16 mOhm High Side Switch |

| MC16Z1CFC25B1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC16Z1CPV20B1 | 制造商:Rochester Electronics LLC 功能描述:16 BIT MCU, 1K RAM - Bulk |

| MC16Z3BCAG16 | 功能描述:16位微控制器 - MCU 16BIT MCU 4KRAM 8KROM RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT |

| MC-17 | 功能描述:TERM BARRIER 17CIRC DUAL ROW RoHS:是 类别:连接器,互连式 >> 接线座 - 隔板块 系列:M 标准包装:10 系列:Beau™ 38780 端接块类型:阻隔块 电路数:15 导线入口数目:30 间距:0.438"(11.12mm) 行数:2 电流:15A 电压:300V 线规:14-22 AWG 顶部端子:螺钉 底部端子:焊片 阻挡层类型:双壁(双) 特点:法兰 颜色:黑 包装:散装 安装类型:通孔 工作温度:- 材料 - 绝缘体:聚对苯二甲酸丁二酯(PBT),玻璃纤维增强型 材料可燃性额定值:UL94 V-0 其它名称:038780-111538780-1115387801115 |

发布紧急采购,3分钟左右您将得到回复。