- 您现在的位置:买卖IC网 > PDF目录98011 > MC56F8033VLC (FREESCALE SEMICONDUCTOR INC) 16-BIT, FLASH, 32 MHz, MICROCONTROLLER, PQFP32 PDF资料下载

参数资料

| 型号: | MC56F8033VLC |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, FLASH, 32 MHz, MICROCONTROLLER, PQFP32 |

| 封装: | ROHS COMPLIANT, PLASTIC, LQFP-32 |

| 文件页数: | 6/157页 |

| 文件大小: | 2117K |

| 代理商: | MC56F8033VLC |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页

Power-Saving Modes

56F8033/56F8023 Data Sheet, Rev. 6

Freescale Semiconductor

103

6.5 Power-Saving Modes

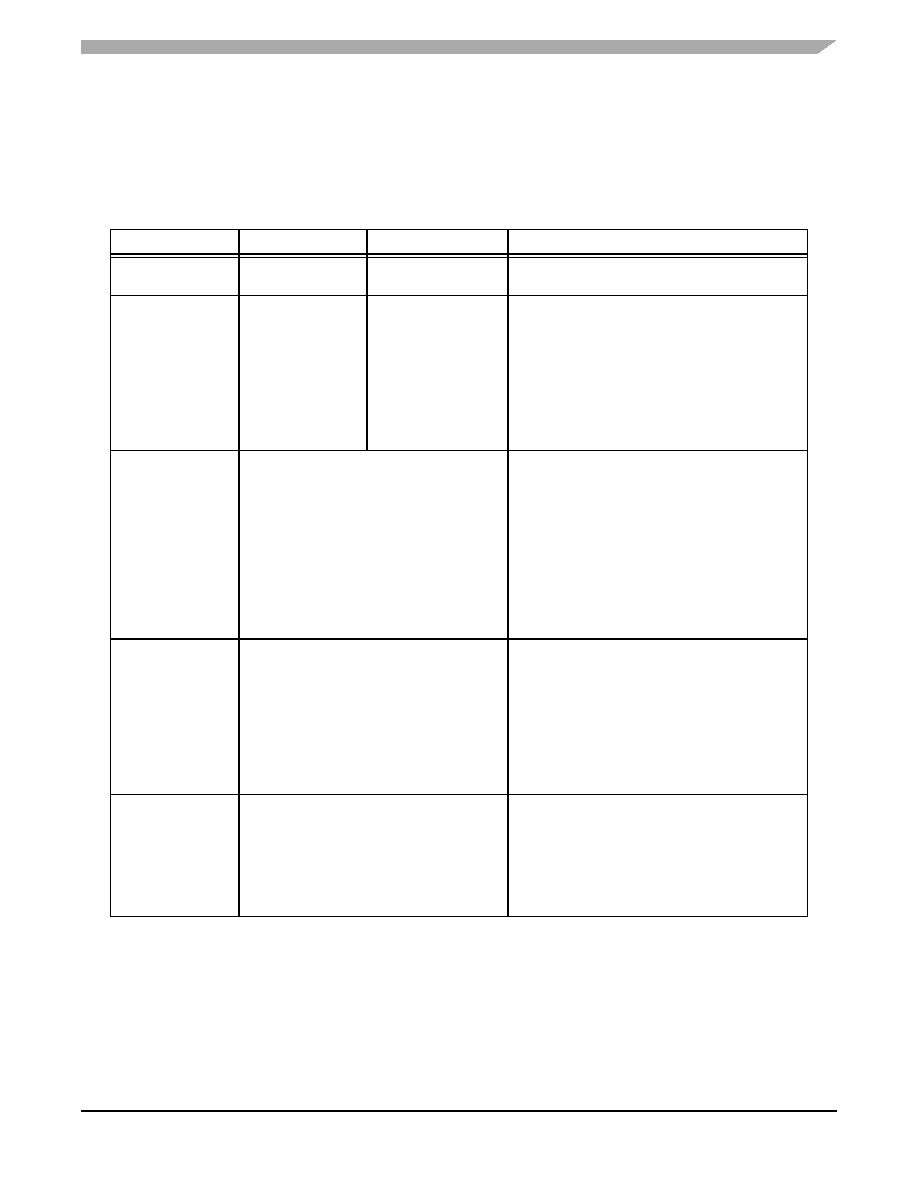

The 56F8033/56F8023 operates in one of five Power-Saving modes, as shown in Table 6-2

The power-saving modes provide additional power management options by disabling the clock,

reconfiguring the voltage regulator clock generation to manage power utilization, as shown in Table 6-2.

Run, Wait, and Stop modes provide methods of enabling/disabling the peripheral and/or core clocking as

a group. Stop disable controls for an individual peripheral are provided in the SDn registers to override the

Table 6-2 Clock Operation in Power-Saving Modes

Mode

Core Clocks

Peripheral Clocks

Description

Run

Core and memory

clocks enabled

Peripheral clocks

enabled

Device is fully functional

Wait

Core and memory

clocks disabled

Peripheral clocks

enabled

Core executes WAIT instruction to enter this

mode.

Typically used for power-conscious applications.

Possible recoveries from Wait mode to Run

mode are:

1. Any interrupt

2. Executing a Debug mode entry command

during the 56800E core JTAG interface

3. Any reset (POR, external, software, COP)

Stop

Master clock generation in the OCCS

remains operational, but the SIM disables

the generation of system and peripheral

clocks.

Core executes STOP instruction to enter this

mode.

Possible recoveries from Stop mode to Run

mode are:

1. Interrupt from any peripheral configured in the

CTRL register to operate in Stop mode (TA0-3,

QSCI0, PIT0-1, CAN, CMPA-B)

2. Low-voltage interrupt

3. Executing a Debug mode entry command

using the 56800E core JTAG interface

4. Any reset (POR, external, software, COP)

Standby

The OCCS generates the master clock at a

reduced frequency (400kHz). The PLL is

disabled and the high-speed peripheral

option is not available. System and

peripheral clocks operate at 200kHz.

The user configures the OCCS and SIM to select

the relaxation oscillator clock source (PRECS),

shut down the PLL (PLLPD), put the relaxation

oscillator in Standby mode (ROSB), and put the

large regulator in Standby (LRSTDBY). The

device is fully operational, but operating at a

minimum frequency and power configuration.

Recovery requires reversing the sequence used

to enter this mode (allowing for PLL lock time).

Power-Down

Master clock generation in the OCCS is

completely shut down. All system and

peripheral clocks are disabled.

The user configures the OCCS and SIM to enter

Standby mode as shown in the previous

description, followed by powering down the

oscillator (ROPD). The only possible recoveries

from this mode are:

1. External Reset

2. Power-On Reset

相关PDF资料 |

PDF描述 |

|---|---|

| MC56F8347MPY60 | 16-BIT, 120 MHz, OTHER DSP, PQFP160 |

| MC56F8355VFG60 | 4-BIT, 120 MHz, OTHER DSP, PQFP128 |

| MC56F8355MFG60 | 4-BIT, 120 MHz, OTHER DSP, PQFP128 |

| MC6805R2CP | 8-BIT, MROM, MICROCONTROLLER, PDIP40 |

| MC68302PV25C | LOCAL AREA NETWORK CONTROLLER, PQFP144 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC56F8035VLD | 功能描述:数字信号处理器和控制器 - DSP, DSC 16 BIT DSPHC 64KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| MC56F8035VLDR | 功能描述:数字信号处理器和控制器 - DSP, DSC 16 BIT DSPHC 64KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| MC56F8036 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| MC56F8036VLF | 功能描述:数字信号处理器和控制器 - DSP, DSC 16 BIT DSPHC RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| MC56F8036VLF | 制造商:Freescale Semiconductor 功能描述:IC DSC 64KB 32MHZ 3.6V LQFP-48 |

发布紧急采购,3分钟左右您将得到回复。