- 您现在的位置:买卖IC网 > PDF目录20357 > MCZ33937EK (Freescale Semiconductor)IC PRE-DRIVER 3PHASE 54-SOIC PDF资料下载

参数资料

| 型号: | MCZ33937EK |

| 厂商: | Freescale Semiconductor |

| 文件页数: | 31/48页 |

| 文件大小: | 0K |

| 描述: | IC PRE-DRIVER 3PHASE 54-SOIC |

| 标准包装: | 26 |

| 系列: | SMARTMOS™ |

| 配置: | 3 相桥 |

| 输入类型: | 非反相 |

| 延迟时间: | 265ns |

| 电流 - 峰: | 600mA |

| 配置数: | 1 |

| 输出数: | 3 |

| 高端电压 - 最大(自引导启动): | 15V |

| 电源电压: | 8 V ~ 40 V |

| 工作温度: | -40°C ~ 135°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 54-BSSOP(0.295",7.50mm 宽)裸露焊盘 |

| 供应商设备封装: | 54-SOICW-EP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

�� �

�

FUNCTIONAL� DEVICE� OPERATION�

�LOGIC� COMMANDS� AND� REGISTERS�

�LOGIC� COMMANDS� AND� REGISTERS�

�COMMAND� DESCRIPTIONS�

�The� IC� contains� internal� registers� to� control� the� various�

�operating� parameters,� modes,� and� interrupt� characteristics.�

�These� commands� are� sent� and� status� is� read� via� 8-bit� SPI�

�commands.� The� IC� will� use� the� last� eight� bits� in� an� SPI�

�transfer,� so� devices� can� be� daisy-chained.� The� first� three� bits�

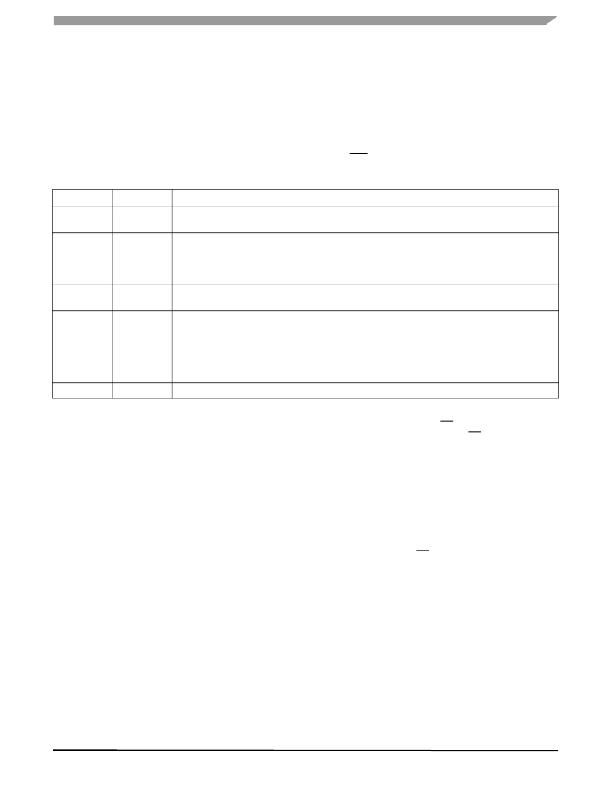

�Table� 7.� Command� List�

�in� an� SPI� word� can� be� considered� to� be� the� Command� with�

�the� trailing� five� bits� being� the� data.�

�The� SPI� logic� will� generate� a� framing� error� and� ignore� the�

�SPI� message� if� the� number� of� received� bits� is� not� eight� or� if� it�

�is� not� a� multiple� of� eight.�

�After� RST,� the� first� SPI� result� returned� is� Status� Register� 0.�

�Command�

�000x� xxxx�

�0010� xxxx�

�0011� xxxx�

�010x� xxxx�

�0110� xxxx�

�0111� xxxx�

�100x� xxxx�

�Name�

�NULL�

�MASK0�

�MASK1�

�MODE�

�CLINT0�

�CLINT1�

�DEADTIME�

�Description�

�These� commands� are� used� to� read� IC� status.� These� commands� do� not� change� any� internal� IC� status.� Returns�

�Status� Register� 0-3,� depending� on� sub� command.�

�Sets� a� portion� of� the� interrupt� mask� using� lower� four� bits� of� command.� A� “1”� bit� enables� interrupt� generation�

�for� that� flag.� INT� remains� asserted� if� uncleared� faults� are� still� present.� Returns� Status� Register� 0.�

�Sets� a� portion� of� the� interrupt� mask� using� lower� four� bits� of� command.� A� “1”� bit� enables� interrupt� generation�

�for� that� flag.� INT� remains� asserted� if� uncleared� faults� are� still� present.� Returns� Status� Register� 0.�

�Enables� Desat/Phase� Error� Mode.� Enables� FULLON� Mode.� Locks� further� Mode� changes.� Returns� Status�

�Register� 0.�

�Clears� a� portion� of� the� fault� latch� corresponding� to� MASK0� using� lower� four� bits� of� command.� A� 1� bit� clears�

�the� interrupt� latch� for� that� flag.� INT� remains� asserted� if� other� unmasked� faults� are� still� present.� Returns� Status�

�Register� 0.�

�Clears� a� portion� of� the� fault� latch� corresponding� to� MASK1� using� lower� four� bits� of� command.� A� 1� bit� clears�

�the� interrupt� latch� for� that� flag.� INT� remains� asserted� if� other� unmasked� faults� are� still� present.� Returns� Status�

�Register� 0.�

�Set� deadtime� with� calibration� technique.� Returns� Status� Register� 0.�

�FAULT� REPORTING� AND� INTERRUPT�

�GENERATION�

�Different� fault� conditions� described� in� the� previous�

�chapters� can� generate� an� interrupt� -� INT� pin� output� signal�

�asserted� high.� When� an� interrupt� occurs,� the� source� can� be�

�read� from� Status� Register� 0,� which� is� also� the� return� word� of�

�most� SPI� messages.�

�Faults� are� latched� on� occurrence,� and� the� interrupt� and�

�faults� are� only� cleared� by� sending� the� corresponding� CLINTx�

�command.� A� fault� that� still� exists� will� continue� to� assert� an�

�interrupt.�

�Note:� If� there� are� multiple� pending� interrupts,� the� INT� line�

�will� not� toggle� when� one� of� the� faults� is� cleared.� Interrupt�

�processing� circuitry� on� the� host� must� be� level� sensitive� to�

�correctly� detect� multiple� simultaneous� interrupt.�

�Thus,� when� an� interrupt� occurs,� the� host� can� query� the� IC�

�indicating� any� faults� not� cleared� since� the� CLINTx� command�

�was� last� written� (rising� edge� of� CS)� and� the� beginning� of� the�

�current� SPI� command� (falling� edge� of� CS).� The� NULL�

�command� causes� no� changes� to� the� state� of� any� of� the� fault�

�or� mask� bits.�

�The� logic� clearing� the� fault� latches� occurs� only� when:�

�1.� A� valid� command� had� been� received(i.e.� no� framing�

�error);�

�2.� A� state� change� did� not� occur� during� the� SPI� message�

�(if� the� bit� is� being� returned� as� a� 0� and� a� fault� change�

�occurs� during� the� middle� of� the� SPI� message,� the� latch�

�will� remain� set).� The� latch� is� cleared� on� the� trailing�

�(rising)� edge� of� the� CS� pulse.� Note,� to� prevent� missing�

�any� faults� the� CLINTx� command� should� not� generally�

�clear� any� faults� without� being� observed;� i.e.� it� should�

�only� clear� faults� returned� in� the� prior� NULL� response.�

�by� sending� a� NULL� command;� the� return� word� contains� flags�

�33937A�

�Analog� Integrated� Circuit� Device� Data�

�Freescale� Semiconductor�

�31�

�相关PDF资料 |

PDF描述 |

|---|---|

| 345-100-527-204 | CARDEDGE 100POS DUAL .100 GREEN |

| T95D107K016LSAS | CAP TANT 100UF 16V 10% 2917 |

| HCC05DRTS-S13 | CONN EDGECARD 10POS .100 EXTEND |

| VI-264-CX-S | CONVERTER MOD DC/DC 48V 75W |

| 345-100-527-202 | CARDEDGE 100POS DUAL .100 GREEN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MCZ33937EK/R2 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Three Phase Field Effect Transistor Pre-driver |

| MCZ33937EKR2 | 功能描述:功率驱动器IC THREE PHASE PRE DRIVER RoHS:否 制造商:Micrel 产品:MOSFET Gate Drivers 类型:Low Cost High or Low Side MOSFET Driver 上升时间: 下降时间: 电源电压-最大:30 V 电源电压-最小:2.75 V 电源电流: 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8 封装:Tube |

| MCZ33970EG | 功能描述:马达/运动/点火控制器和驱动器 DUAL GAGE DRVR IMP DAMP RoHS:否 制造商:STMicroelectronics 产品:Stepper Motor Controllers / Drivers 类型:2 Phase Stepper Motor Driver 工作电源电压:8 V to 45 V 电源电流:0.5 mA 工作温度:- 25 C to + 125 C 安装风格:SMD/SMT 封装 / 箱体:HTSSOP-28 封装:Tube |

| MCZ33970EG | 制造商:Freescale Semiconductor 功能描述:IC STEPPER MOTOR GAUGE DRIVER SPI |

| MCZ33970EGR2 | 功能描述:马达/运动/点火控制器和驱动器 DUAL GAGE DRVR IMP DAMP RoHS:否 制造商:STMicroelectronics 产品:Stepper Motor Controllers / Drivers 类型:2 Phase Stepper Motor Driver 工作电源电压:8 V to 45 V 电源电流:0.5 mA 工作温度:- 25 C to + 125 C 安装风格:SMD/SMT 封装 / 箱体:HTSSOP-28 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。