- 您现在的位置:买卖IC网 > PDF目录363669 > NT5DS32M8AW-75B (Electronic Theatre Controls, Inc.) 256Mb Double Data Rate SDRAM PDF资料下载

参数资料

| 型号: | NT5DS32M8AW-75B |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 256Mb Double Data Rate SDRAM |

| 中文描述: | 256MB双数据速率SDRAM |

| 文件页数: | 15/78页 |

| 文件大小: | 1534K |

| 代理商: | NT5DS32M8AW-75B |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页

NT5DS64M4AT NT5DS64M4AW

NT5DS32M8AT NT5DS32M8AW

256Mb Double Data Rate SDRAM

REV 1.1

12/2001

15

NANYA TECHNOLOGY CORP

. All rights reserved.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

Commands

Truth Tables 1a and 1b provide a reference of the commands supported by DDR SDRAM devices. A verbal description of each

commands follows.

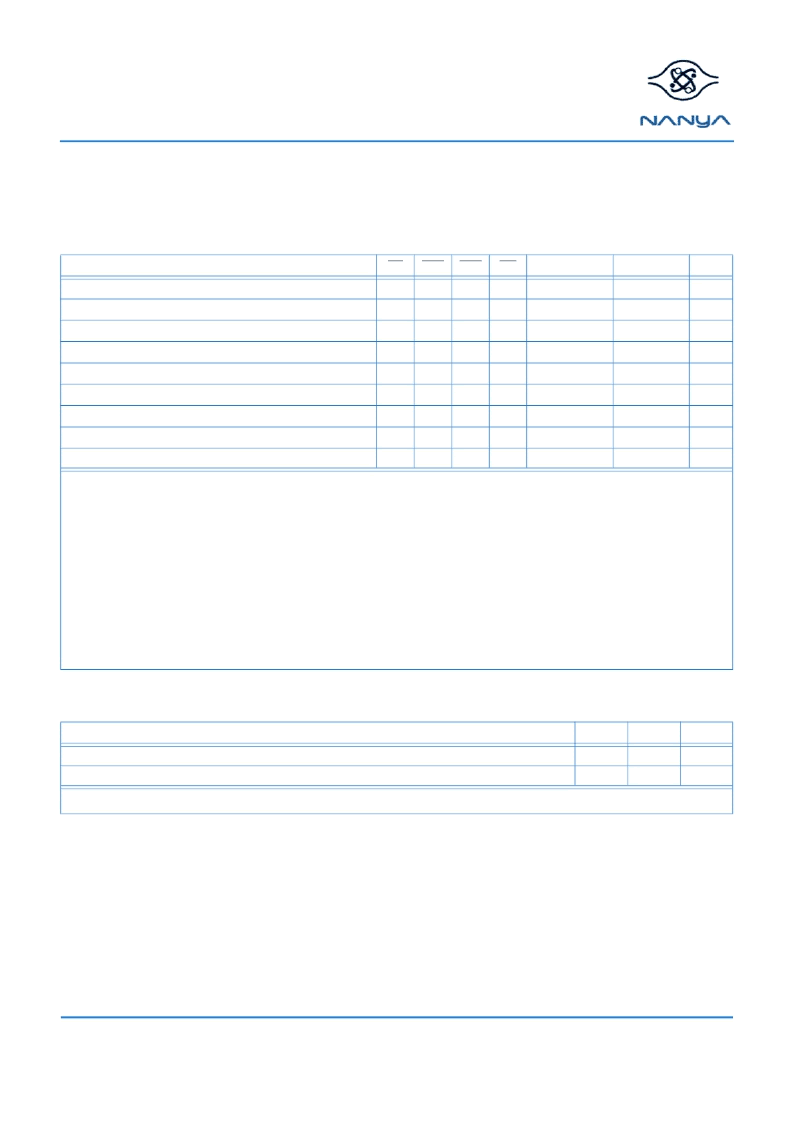

Truth Table 1a: Commands

Name (Function)

CS

RAS

CAS

WE

Address

MNE

Notes

Deselect (Nop)

H

X

X

X

X

NOP

1, 9

No Operation (Nop)

L

H

H

H

X

NOP

1, 9

Active (Select Bank And Activate Row)

L

L

H

H

Bank/Row

ACT

1, 3

Read (Select Bank And Column, And Start Read Burst)

L

H

L

H

Bank/Col

Read

1, 4

Write (Select Bank And Column, And Start Write Burst)

L

H

L

L

Bank/Col

Write

1, 4

Burst Terminate

L

H

H

L

X

BST

1, 8

Precharge (Deactivate Row In Bank Or Banks)

L

L

H

L

Code

PRE

1, 5

Auto Refresh Or Self Refresh (Enter Self Refresh Mode)

L

L

L

H

X

AR / SR

1, 6, 7

Mode Register Set

L

L

L

L

Op-Code

MRS

1, 2

1. CKE is high for all commands shown except Self Refresh.

2. BA0, BA1 select either the Base or the Extended Mode Register (BA0 = 0, BA1 = 0 selects Mode Register; BA0 = 1, BA1 = 0 selects

Extended Mode Register; other combinations of BA0-BA1 are reserved; A0-A12 provide the op-code to be written to the selected Mode

Register.)

3. BA0-BA1 provide bank address and A0-A12 provide row address.

4. BA0, BA1 provide bank address; A0-A

i

provide column address (where

i

= 9 for x8 and 9, 11 for x4); A10 high enables the Auto Pre-

charge feature (nonpersistent), A10 low disables the Auto Precharge feature.

5. A10 LOW: BA0, BA1 determine which bank is precharged.

A10 HIGH: all banks are precharged and BA0, BA1 are “Don’t Care.”

6. This command is auto refreshif CKE is high; Self Refresh if CKE is low.

7. Internal refresh counter controls row and bank addressing; all inputs and I/Os are “Don’t Care” except for CKE.

8. Applies only to read bursts with Auto Precharge disabled; this command is undefined (and should not be used) for read bursts with Auto

Precharge enabled or for write bursts

9. Deselect and NOP are functionally interchangeable.

Truth Table 1b: DM Operation

Name (Function)

DM

DQs

Notes

Write Enable

L

Valid

1

Write Inhibit

H

X

1

1. Used to mask write data; provided coincident with the corresponding data.

相关PDF资料 |

PDF描述 |

|---|---|

| NT5DS32M8AW-7K | 256Mb Double Data Rate SDRAM |

| NT5DS32M8AW-8B | 256Mb Double Data Rate SDRAM |

| NT5DS64M4AW-75B | 256Mb Double Data Rate SDRAM |

| NT5DS64M4AW-7K | 256Mb Double Data Rate SDRAM |

| NT5DS64M4AW-8B | 256Mb Double Data Rate SDRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| NT5DS32M8AW-7K | 制造商:未知厂家 制造商全称:未知厂家 功能描述:256Mb Double Data Rate SDRAM |

| NT5DS32M8AW-8B | 制造商:未知厂家 制造商全称:未知厂家 功能描述:256Mb Double Data Rate SDRAM |

| NT5DS32M8CS | 制造商:NANOAMP 制造商全称:NANOAMP 功能描述:256Mb DDR Synchronous DRAM |

| NT5DS32M8CS-5T | 制造商:NANOAMP 制造商全称:NANOAMP 功能描述:256Mb DDR Synchronous DRAM |

| NT5DS32M8CS-6K | 制造商:NANOAMP 制造商全称:NANOAMP 功能描述:256Mb DDR Synchronous DRAM |

发布紧急采购,3分钟左右您将得到回复。