- 您现在的位置:买卖IC网 > PDF目录363669 > NT5DS32M8AW-75B (Electronic Theatre Controls, Inc.) 256Mb Double Data Rate SDRAM PDF资料下载

参数资料

| 型号: | NT5DS32M8AW-75B |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 256Mb Double Data Rate SDRAM |

| 中文描述: | 256MB双数据速率SDRAM |

| 文件页数: | 17/78页 |

| 文件大小: | 1534K |

| 代理商: | NT5DS32M8AW-75B |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页

NT5DS64M4AT NT5DS64M4AW

NT5DS32M8AT NT5DS32M8AW

256Mb Double Data Rate SDRAM

REV 1.1

12/2001

17

NANYA TECHNOLOGY CORP

. All rights reserved.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

Auto Precharge

Auto Precharge is a feature which performs the same individual-bank precharge function described above, but without requiring

an explicit command. This is accomplished by using A10 to enable Auto Precharge in conjunction with a specific Read or Write

command. A precharge of the bank/row that is addressed with the Read or Write command is automatically performed upon

completion of the Read or Write burst. Auto Precharge is nonpersistent in that it is either enabled or disabled for each individual

Read or Write command. Auto Precharge ensures that the precharge is initiated at the earliest valid stage within a burst. This is

determined as if an explicit Precharge command was issued at the earliest possible time without violating t

RAS

(min). The user

must not issue another command to the same bank until the precharge (t

RP

) is completed.

The NTC DDR SDRAM devices supports the optional t

RAS

lockout feature. This feature allows a Read command with Auto Pre-

charge to be issued to a bank that has been activated (opened) but has not yet satisfied the t

RAS

(min) specification. The t

RAS

lockout feature essentially delays the onset of the auto precharge operation until two conditions occur. One, the entire burst

length of data has been successfully prefetched from the memory array; and two, t

RAS

(min) has been satisfied.

As a means to specify whether a DDR SDRAM device supports the t

RAS

lockout feature, a new parameter has been defined,

t

RAP

(RAS Command to Read Command with Auto Precharge or better stated Bank Activate to Read Command with Auto Pre-

charge). For devices that support the t

RAS

lockout feature, t

RAP

= t

RCD

(min). This allows any Read Command (with or without

Auto Precharge) to be issued to an open bank once t

RCD

(min) is satisfied.

Burst Terminate

The Burst Terminate command is used to truncate read bursts (with Auto Precharge disabled). The most re-cently registered

Read command prior to the Burst Terminate command is truncated, as shown in the Operation section of this data sheet. Write

burst cycles are not to be terminated with the Burst Terminate command.

t

RAP

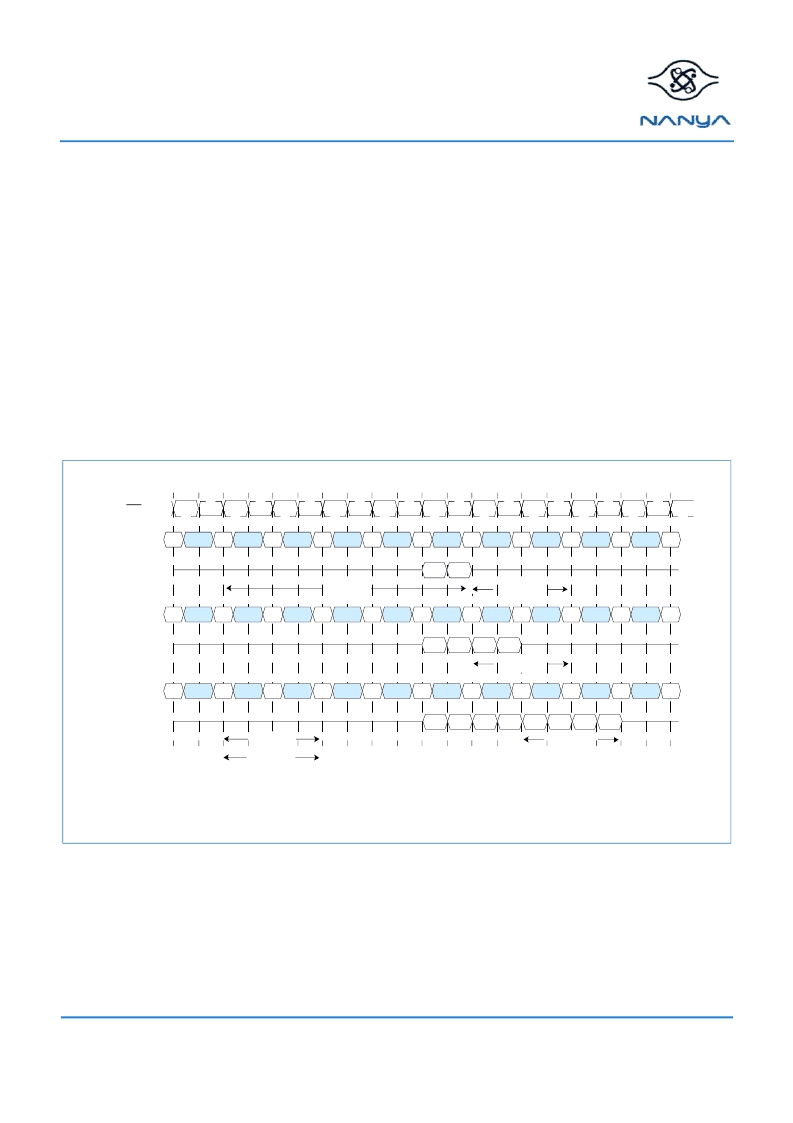

Definition

CK

CK

Command

DQ (BL=2)

t

RAPmin

NOP

ACT

NOP

RD A

NOP

NOP

NOP

NOP

ACT

NOP

NOP

t

RCDmin

t

RASmin

DQ0

DQ1

The above timing diagrams show the effects of t

for devices that support t

with Auto Precharge command (RDA) is issued with t

(min) and dataout is available with the shortest latency from the

Bank Activate command (ACT). The internal precharge operation, however, does not begin until after t

RAS

(min) is satisfied.

CL=2, t

CK

=10ns

Command

DQ (BL=4)

NOP

ACT

NOP

RD A

NOP

NOP

NOP

*

NOP

ACT

NOP

NOP

DQ0

DQ1

DQ2

DQ3

t

RPmin

Command

DQ (BL=8)

NOP

ACT

NOP

RD A

NOP

NOP

*

NOP

NOP

ACT

NOP

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

t

RPmin

DQ6

DQ7

*

*

Indicates Auto Precharge begins here

t

RPmin

相关PDF资料 |

PDF描述 |

|---|---|

| NT5DS32M8AW-7K | 256Mb Double Data Rate SDRAM |

| NT5DS32M8AW-8B | 256Mb Double Data Rate SDRAM |

| NT5DS64M4AW-75B | 256Mb Double Data Rate SDRAM |

| NT5DS64M4AW-7K | 256Mb Double Data Rate SDRAM |

| NT5DS64M4AW-8B | 256Mb Double Data Rate SDRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| NT5DS32M8AW-7K | 制造商:未知厂家 制造商全称:未知厂家 功能描述:256Mb Double Data Rate SDRAM |

| NT5DS32M8AW-8B | 制造商:未知厂家 制造商全称:未知厂家 功能描述:256Mb Double Data Rate SDRAM |

| NT5DS32M8CS | 制造商:NANOAMP 制造商全称:NANOAMP 功能描述:256Mb DDR Synchronous DRAM |

| NT5DS32M8CS-5T | 制造商:NANOAMP 制造商全称:NANOAMP 功能描述:256Mb DDR Synchronous DRAM |

| NT5DS32M8CS-6K | 制造商:NANOAMP 制造商全称:NANOAMP 功能描述:256Mb DDR Synchronous DRAM |

发布紧急采购,3分钟左右您将得到回复。