- 您现在的位置:买卖IC网 > PDF目录189449 > OR3L225B7PS680-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 1444 CLBS, 166000 GATES, 266.4 MHz, PBGA680 PDF资料下载

参数资料

| 型号: | OR3L225B7PS680-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1444 CLBS, 166000 GATES, 266.4 MHz, PBGA680 |

| 封装: | PLASTIC, BGAM-680 |

| 文件页数: | 37/77页 |

| 文件大小: | 873K |

| 代理商: | OR3L225B7PS680-DB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页

42

PD78052, 78053, 78054, 78055, 78056, 78058

Data Sheet U12327EJ5V0DS00

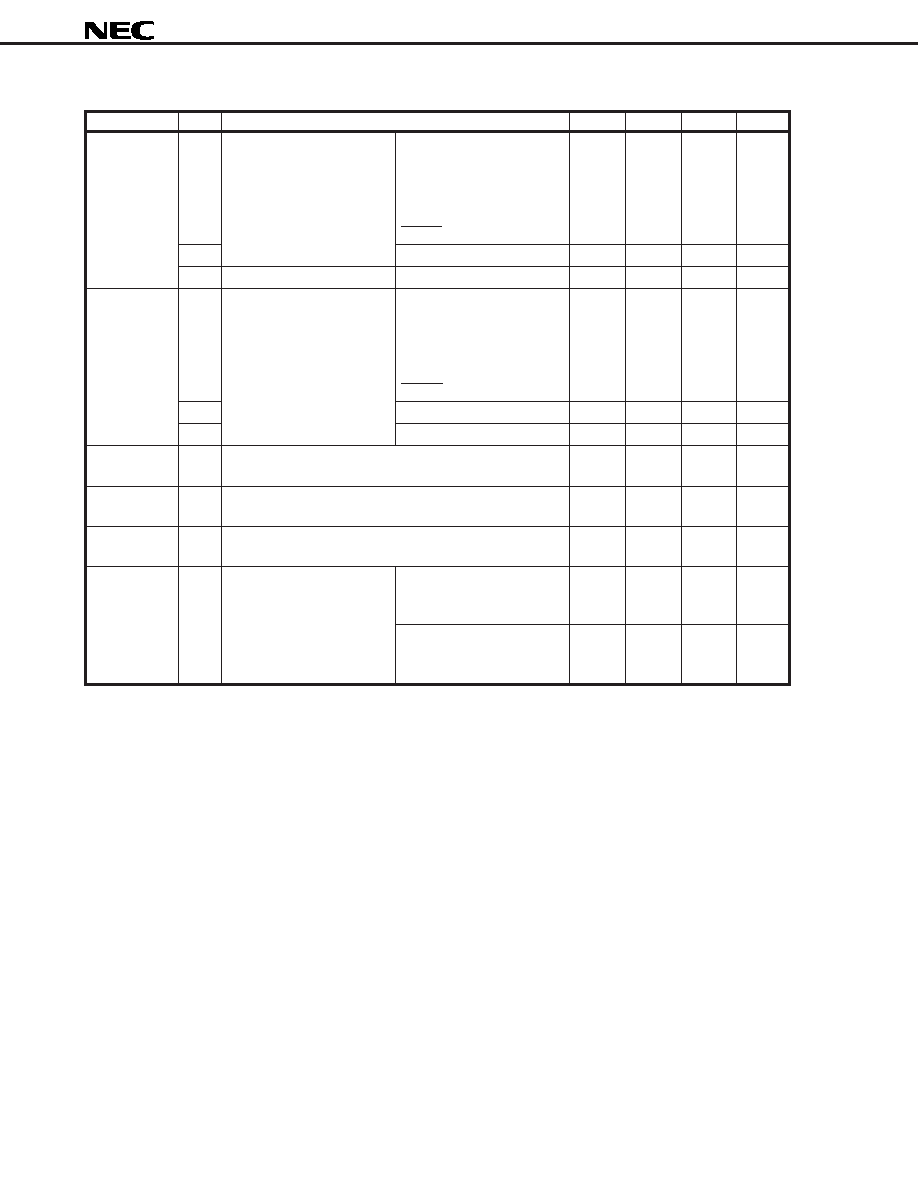

DC Characteristics (TA = –40 to +85

°C, VDD = 2.0 to 6.0 V)

Parameter

Symbol

Conditions

MIN.

TYP.

MAX.

Unit

Input leakage

ILIH1

VIN = VDD

P00 to P06, P10 to P17,

3

A

current, high

P20 to P27, P30 to P37,

P40 to P47, P50 to P57,

P60 to P67, P70 to P72,

P120 to P127, P130, P131,

RESET

ILIH2

X1, X2, XT1/P07, XT2

20

A

ILIH3

VIN = 15 V

P60 to P63

80

A

Input leakage

ILIL1

VIN = 0 V

P00 to P06, P10 to P17,

–3

A

current, low

P20 to P27, P30 to P37,

P40 to P47, P50 to P57,

P64 to P67, P70 to P72,

P120 to P127, P130, P131,

RESET

ILIL2

X1, X2, XT1/P07, XT2

–20

A

ILIL3

P60 to P63

–3 Note 1

A

Output leakage

ILOH

VOUT = VDD

3

A

current, high

Output leakage

ILOL

VOUT = 0 V

–3

A

current, low

Mask option

R1

VIN = 0 V, P60 to P63

20

40

90

k

pull-up resistor

Software

R2

VIN = 0 V, P01 to P06,

4.5 V

≤ VDD ≤ 6.0 V

15

40

90

k

pull-up

P10 to P17, P20 to P27,

resistorNote 2

P30 to P37, P40 to P47,

P50 to P57, P64 to P67,

2.7 V

≤ VDD < 4.5 V

20

500

k

P70 to P72, P120 to

P127, P130, P131

Notes 1. When pull-up resistors are not connected to P60 to P63 (specifiable by the mask option), a low-level input

leakage current of –200

A (MAX.) flows only for 1.5 clocks (without wait) after a read instruction has been

executed to port 6 (P6) or port mode register 6 (PM6). At times other than this 1.5-clock interval, a –3

A

(MAX.) current flows.

2. A software pull-up resistor can be used only in the range of VDD = 2.7 to 6.0 V.

Remark

Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

相关PDF资料 |

PDF描述 |

|---|---|

| OR3L225B7PS680I-DB | FPGA, 1444 CLBS, 166000 GATES, 266.4 MHz, PBGA680 |

| OR3L225B8PS432-DB | FPGA, 1444 CLBS, 166000 GATES, 333 MHz, PBGA432 |

| OR3L225B8PS680-DB | FPGA, 1444 CLBS, 166000 GATES, 333 MHz, PBGA680 |

| OR3L225B7BC432-DB | FPGA, 1444 CLBS, 166000 GATES, 266.4 MHz, PBGA432 |

| OR3L225B8BC432-DB | FPGA, 1444 CLBS, 166000 GATES, 333 MHz, PBGA432 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| OR3L225B8BC432-DB | 功能描述:FPGA - 现场可编程门阵列 11552 LUT 612 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR3L225B8BM680-DB | 功能描述:FPGA - 现场可编程门阵列 11552 LUT 612 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR3LP26B | 制造商:AGERE 制造商全称:AGERE 功能描述:Field-Programmable System Chip (FPSC) Embedded Master/Target PCI Interface |

| OR3LP26BBA352-DB | 功能描述:FPGA - 现场可编程门阵列 FPSC PCI INTERFACE RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR3LP26BBM680-DB | 功能描述:FPGA - 现场可编程门阵列 FPSC PCI INTERFACE RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。